Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2013] | [2014] | [2015] | [2016] | [2017] | [2018] | [2019] | [Japanese] / [English]

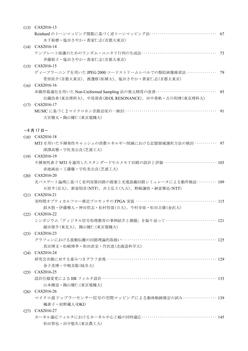

CAS2016-1

Hardware Trojan Identification based on Netlist Features using Neural Networks

Kento Hasegawa, Masao Yanagisawa, Nozomu Togawa (Waseda Univ.)

pp. 1 - 6

CAS2016-2

Verification Experiment of Scan-based Attack against a Trivium Cipher Circut

Daisuke Oku, Masao Yanagisawa, Nozomu Togawa (Waseda Univ.)

pp. 7 - 12

CAS2016-3

Automatic Test Pattern Generation for Multiple Stuck-At Faults: When Testing for Single Faults is Insufficient

Conrad JinYong Moore, Amir Masoud Gharehbaghi, Masahiro Fujita (Univ. of Tokyo)

pp. 13 - 18

CAS2016-4

On random test pattern generation algorithm considering signal transition activities

Yusuke Matsunaga (Kyushu Univ.)

pp. 19 - 22

CAS2016-5

A descriptor system representation of circuit equations based on the reduced incidence matrix

Daisuke Saito, Toshikazu Sekine, Yasuhiro Takahashi (Gifu Univ.)

pp. 23 - 28

CAS2016-6

Hardware Implementation of Stochastic Gammatone Filter

Naoya Onizawa, Shunsuke Koshita, Shuichi Sakamoto, Masahide Abe, Masayuki Kawamata, Takahiro Hanyu (Tohoku Univ.)

pp. 29 - 34

CAS2016-7

A method of reducing amount of operations on the bit serial multiply-accumulator and its application

Daichi Okamoto (Okayama Prefectural Univ.), Masafumi Kondo (Kawasaki Univ. of Medical Welfare), Yoshihiro Sejima, Tomoyuki Yokogawa, Kazutami Arimoto, Yoichiro Sato (Okayama Prefectural Univ.)

pp. 35 - 40

CAS2016-8

Significance Analysis for Edges in a Graph by means of Leveling Variables on Nodes

Kento Hamada, Norihiko Shinomiya (Soka Univ.)

pp. 41 - 45

CAS2016-9

[Panel Discussion]

The Role of System and Signal Processing Subsociety

-- Encouragement and Development of Young Researchers --

Yoshinobu Kajikawa (Kansai Univ.), Shunsuke Koshita (Tohoku Univ.), Takashi Takenaka (NEC), Yuichi Tanaka (TUAT), Satoshi Yamane (Kanazawa Univ.)

p. 47

CAS2016-10

Spectral Analysis of Universal Register Machine on Game of LIFE

Shigeru Ninagawa (KIT)

pp. 49 - 54

CAS2016-11

A Strategy for AP Selection with Mutual Concession in Sustainable Heterogeneous Wireless Networks

Hideo Kobayashi, Eiichi Kameda, Yoshiaki Terashima, Norihiko Shinomiya (Soka Univ.)

pp. 55 - 60

CAS2016-12

Controllability Analysis of Boolean Networks Focusing on Attractors

Koichi Kobayashi (Hokkaido Univ.)

pp. 61 - 66

CAS2016-13

Inverse Tone Mapping Based on Reinhard's Tone Mapping Operator

Yuma Kinoshita, Sayaka Shiota, Hitoshi Kiya (Tokyo Metro. Univ.)

pp. 67 - 72

CAS2016-14

A generation scheme of random unitary matrices for template protection

Yuko Saito, Sayaka Shiota, Hitoshi Kiya (Tokyo Metropolitan Univ.)

pp. 73 - 78

CAS2016-15

Image retrieval in JPEG 2000 codestream domain by a deep learning approach

Yusuke Sugawara (Tokyo Metropolitan Univ), Osamu Watanabe (Takushoku Univ), Sayaka Shiota, Hitoshi Kiya (Tokyo Metropolitan Univ)

pp. 79 - 84

CAS2016-16

Improvement of restore accuracy of the Non-Uniformed Sampling method using nonlinear optimization

Koki Degura (Tokyo Univ of Science), Tomoki Nakao (JEOL RESONANCE Co., Ltd.), Yuho Tanaka, Toshihiro Furukawa (Tokyo Univ of Science)

pp. 85 - 89

CAS2016-17

A Study on Sound Source Tracking via Two Microphones Based on MUSIC

Kenta Omiya, Kenji Suyama (Tokyo Denki Univ.)

pp. 91 - 96

CAS2016-18

Line selection to reduce store-energy in MTJ-based non-volatile caches

Takamasa Fukasawa, Kimiyoshi Usami (SIT)

pp. 97 - 102

CAS2016-19

Design and Evaluation of MTJ-based Standard Cell Memory

Junya Akaike, Masaru Kudo, Kimiyoshi Usami (SIT)

pp. 103 - 108

CAS2016-20

A Parallel Adder Circuit based on Optical Pass-gate Logic and Its Evaluation with Optoelectronic Circuit Simulator

Tohru Ishihara (Kyoto Univ.), Akihiko Shinya (NTT), Koji Inoue (Kyushu Univ.), Kengo Nozaki, Masaya Notomi (NTT)

pp. 109 - 114

CAS2016-21

An FPGA Implementation of Real-time Optical Flow Estimation Processor

Yu Suzuki, Masato Ito, Satoshi Kanda, Tetsuya Matsumura (Nihon Univ.), Kousuke Imamura, Yoshio Matsuda (Kanazawa Univ.)

pp. 115 - 120

CAS2016-22

After the Symposium "Case Studies and Open Problems in Digital Signal Processing Education"

Shunsuke Koshita (Tohoku Univ.), Kenji Suyama (Tokyo Denki Univ.)

pp. 121 - 124

CAS2016-23

Equivalent Circuit Approach for Wave Propagation in Graphene-based Structures

Hirofumi Sanada, Hiroki Matsuzaki, Naofumi Wada, Megumi Takezawa (HUS)

pp. 125 - 128

CAS2016-24

A weighted graph representation for new joint of technical committee conferences

Yoshihiro Kaneko, Katsuaki Nakajima (Gifu Univ.)

pp. 129 - 132

CAS2016-25

A Design Method of IIR Filters by Adjusting Design Specification

Kenzo Yamamoto, Kenji Suyama (Tokyo Denki Univ.)

pp. 133 - 138

CAS2016-26

A Study on Trajectory Estimation using Spatial Mapping of Microwave Doppler Signals

Motoko Tachibana, Kurato Maeno (OKI)

pp. 139 - 144

CAS2016-27

Simultaneous Adaptation of Kernel Centers and Width for Kernel Adaptive Filter

Tomoya Wada, Toshihisa Tanaka (TUAT)

pp. 145 - 150

CAS2016-28

Decoding of Cortical Entrainment when Listening to Natural Music

Yuiko Kumagai, Toshihisa Tanaka (TUAT)

pp. 151 - 156

CAS2016-29

Study on Feedforward ANC system with Virtual sensing technique

Shoma Edamoto, Chuang Shi, Yosinobu Kajikawa (Kansai Univ.)

pp. 157 - 160

CAS2016-30

Decoding of Rhythm Imagery from EEG

Haruki Okawa, Kaori Suefusa, Toshihisa Tanaka (TUAT)

pp. 161 - 166

CAS2016-31

Clock Distribution Network with Multiple Source Buffers for Stacked Chips

Nanako Niioka, Masashi Imai, Kaoru Furumi, Atsushi Kurokawa (Hirosaki Univ.)

pp. 167 - 172

CAS2016-32

Thermal Analysis in 3D ICs

Kaoru Furumi, Masashi Imai, Nanako Niioka, Atsushi Kurokawa (Hirosaki Univ.)

pp. 173 - 178

CAS2016-33

A Study on Fault Tolerant Features of Asynchronous Circuits using Voted-enable Latches

Masashi Imai (Hirosaki Univ.), Tomohiro Yoneda (NII)

pp. 179 - 184

CAS2016-34

Tamper Resistant Asynchronous Pipeline Circuits using Random Delay Elements

Daiki Toyoshima, Atsushi Kurokawa, Masashi Imai (Hirosaki Univ.)

pp. 185 - 190

CAS2016-35

On Study of Data Reliability of Threshold Sensing with Majority Circuit

Akito Hoshide, Bo Liu, Takuro Ishida, Shigetoshi Nakatake (Univ. of Kitakyushu)

pp. 191 - 196

CAS2016-36

Analog Characterization Module based on A/D and D/A Converters

Daishi Isogai, Bo Liu, Futa Yoshinaka, Shigetoshi Nakatake (Univ. of Kitakyushu)

pp. 197 - 202

CAS2016-37

Soft-Coupling Module with A/D and D/A Converters

Futa Yoshinaka, Bo Liu, Daishi Isogai, Shigetoshi Nakatake (univ.kitakyushu)

pp. 203 - 208

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.