Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2008] | [2009] | [2010] | [2011] | [2012] | [2013] | [2014] | [Japanese] / [English]

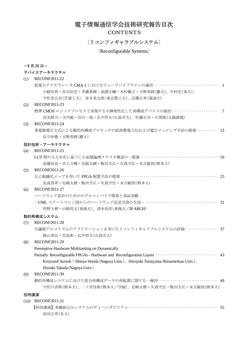

RECONF2011-22

Wavepipelining on A Ultra Low Power Reconfigurable Accelerator CMA-1.

Nobuaki Ozaki, Yoshihiro Yasuda, Yoshiki Saito, Daisuke Ikebuchi, Masayuki Kimura, Hideharu Amano (Keio Univ.), Hiroshi Nakamura (Univ. of Tokyo), Kimiyoshi Usami (Shibaura Inst. of Tech.), Mitaro Namiki (Tokyo Univ. of Agriculture and Tech.), Masaaki Kondo (The Univ. of Electro-Communications)

pp. 1 - 6

RECONF2011-23

Feasibility study of nonvolatile reconfiguralbe device by using a standard CMOS logic process

Shuji Kunimitsu, Mamoru Terauchi, Kazuya Tanigawa, Tetsuo Hironaka (HCU), Masayuki Sato, Takashi Ishiguro (TAIYO YUDEN)

pp. 7 - 12

RECONF2011-24

Low Power Dynamically Reconfigurable Processor with Dual-Vdd/Dual-Vth and its Optimization

Kazuei Hironaka, Hideharu Amano (Keio Univ.)

pp. 13 - 18

RECONF2011-25

A Novel Cluster Structure based on Input Sharing of LUTs

Toshiya Takahashi, Kazuki Inoue, Motoki Amagasaki, Masahiro Iida, Morihiro Kuga, Toshinori Sueyoshi (Kumamoto Univ.)

pp. 19 - 24

RECONF2011-26

FPGA placement based on Self-Organized Map

Yasuaki Tomonari, Motoki Amagasaki, Masahiro Iida, Morihiro Kuga, Toshinori Sueyoshi (Kumamoto Univ.)

pp. 25 - 30

RECONF2011-27

Development Modeling Compiler and Operation Test for the Hardware Design Generate HDL from UML State Machine Diagram

Daiki Kano, Ryota Yamazaki (Tokai Univ.), Naohiko Shimizu (Tokai Univ./IP ARCH, Inc.)

pp. 31 - 36

RECONF2011-28

Evaluation of Reconfigurable Computer System using Application of Parliamentary System

Takahiro Kajiyama, Akira Kojima, Tetsuo Hironaka (HCU)

pp. 37 - 42

RECONF2011-29

Preemptive Hardware Multitasking on Dynamically Partially Reconfigurable FPGAs - Hardware and Reconfiguration Layers

Krzysztof Jozwik, Shinya Honda (Nagoya Univ.), Hiroyuki Tomiyama (Ritsumeikan Univ.), Hiroaki Takada (Nagoya Univ.)

pp. 43 - 48

RECONF2011-30

Relocation of Partial Reconfiguration Data for Dynamic Reconfigurable System

Sadaki Usagawa, Yoshihiro Ichinomiya, Motoki Amagasaki, Morihiro Kuga, Masahiro Iida, Toshinori Sueyoshi (Kumamoto Univ.)

pp. 49 - 54

RECONF2011-31

[Invited Talk]

Dependability of Automotive Embedded Systems

Hiroaki Takada (Nagoya Univ.)

p. 55

RECONF2011-32

Case Studies on an FPGA with System-Level Multiprocessor Design Toolset

Seiya Shibata, Yuki Ando, Shinya Honda (Nagoya Univ.), Hiroyuki Tomiyama (Ritsumeikan Univ.), Hiroaki Takada (Nagoya Univ.)

pp. 57 - 62

RECONF2011-33

A Design Framework for relieving a HW Bottleneck FPGAs Connected with a High-Speed Data Bus

Koichi Araki, Yukinori Sato, Yasushi Inoguchi (JAIST)

pp. 63 - 68

RECONF2011-34

A Basic Implementation of LUT-based Dynamic and Partial Reconfiguration from Remote Site

Hiroyuki Kawai (Hamamatsu Photonics), Moritoshi Yasunaga (Tsukuba Univ.)

pp. 69 - 74

RECONF2011-35

Parallel template matching operations on a dynamically reconfigurable vision-chip architecture

Yuichiro Yamaji (Shizuoka Univ.), Hironari Nakada (Primearth EV Energy), Minoru Watanabe, Shoji Kawahito (Shizuoka Univ.)

pp. 75 - 79

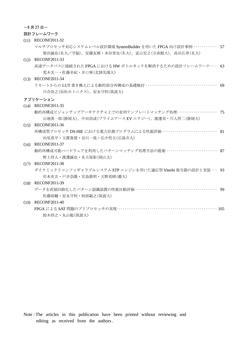

RECONF2011-36

Performance Evaluation of Power Monitoring Programs on Reconfigurable Processor DS-HIE

Kyohei Tao, Takatoshi Tamaoki, Kazuya Tanigawa, Tetsuo Hironaka (Hiroshima City Univ.)

pp. 81 - 86

RECONF2011-37

A proposal of pattern matching techniques using dynamically reconfigurable hardware

Masato Nogami, Nobuya Watanabe, Akira Nagoya (Okayama Univ.)

pp. 87 - 92

RECONF2011-38

Design and Implementation of Adaptive Viterbi Decoder using Dynamic Reconfigurable System STP Engine

Yuken Kishimoto, Takao Toi, Takaaki Miyajima, Hideharu Amano (Keio Univ.)

pp. 93 - 98

RECONF2011-39

Performance Comparison of the Pattern-Recognition Hardware Using Data-Direct-Implementation Approach

Yusuke Sato, Moritoshi Yasunaga, Noriyuki Aibe (Univ. of Tsukuba)

pp. 99 - 104

RECONF2011-40

Variable and Clause Elimination in SAT problems using an FPGA

Masayuki Suzuki, Tsutomu Maruyama (Univ. of Tsukuba)

pp. 105 - 110

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.