# エネルギーハーベストでの利用を想定した 逐次比較型 ADC における PSRR の改善検討

## 時永 征弥<sup>†</sup> 日野 翔太<sup>††</sup> 升井 義博<sup>†</sup> † 広島工業大学工学部電子情報工学科 † † 広島工業大学工学研究科電気電子工学専攻

#### 1. はじめに

近年IoTの発展に伴い、ワイヤレスセンサネットワークが注目されている.無線化の最大の利点は、配線をつなぐ必要がなく低コストであることがあげられる.さらに、エネルギーハーベストの利用で電源線を省くことができればより設置場所の自由度が上がり、一層コストを抑えることが可能となる.しかし、エネルギーハーベストで作り出す電源には安定しないという問題点がある.そこで本稿では、エネルギーハーベストでの利用を想定した際、エッジデバイスに必要不可欠である逐次比較型 ADC のPSRR(電源雑音に対する耐性)改善に関して検討する.

## 2. 逐次比較型 AD 変換器

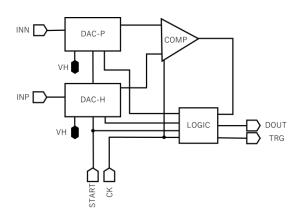

逐次比較型 AD 変換器とは,標本化されたアナログ電圧を DA 変換器からの出力電圧に一致するように逐次比較し,デジタル出力を決定する方式である.この方式は適度に高速かつ低消費電力であるため応用の幅が広く様々なところで利用されている.逐次比較型 AD 変換器の構成を図1に示す.

図1. 逐次比較型 AD 変換器の構成

## 3. 提案回路

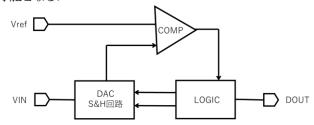

DAC を差動化すことにより、電源電圧の揺れに影響を受けることなく回路を動作させることができる。これによりエネルギーハーベストなどによって得られる不安定な電力供給でも精度の高い動作を保証できる。シングルの非同期型(図2に示す)は、入力電圧と内部 DACの出力を比較して、最上位 bit から順次出力を決定していくのに対して、差動型にすると、2 つの内部 DAC から

COMP に入力される信号の差から回路全体の出力を 決定させるため電源電圧の揺れの影響を抑えることが 可能となる.

図2. シングル非同期型逐次比較 AD 変換器の構成

## 4. シミュレーション結果

$0.18 \, \mu \, \text{m} - \text{CMOS}$  を用い提案する逐次比較型 AD 変換器(8bit)のシミュレーションを行った.電源電圧を1V,サンプリング周波数  $100 \, \text{kHz}$ ,電源電圧に周波数  $30 \, \text{kHz}$ ,  $100 \, \text{mVPP}$  の変動を与え,差動型,非同期型それぞれにおいて性能を比較した.

非同期型[1] 差動型 なし 電源変動 あり なし あり SNR[dB] 47.99 48.24 47.36 23.41 SFDR[dB] 55.00 57.82 55.49 28.47 SNDR[dB] 46.72 47.58 46.87 23.08 ENOB[bit] 7.47 7.61 7.49 3.54

表1. シミュレーション結果

#### 5. 今後の課題

現在は電源電圧変動への影響を考え、PSRR の改善を主として検討したが、エネルギーハーベストで電力を得ることを考えた際、DAC の消費電力を抑える必要がある。 差動化で増加した消費電力を抑えることを今後の課題として研究を進めていく。

### 【謝辞】

本研究は東京大学大規模集積システム設計教育研究センターを通じケイデンス㈱とローム㈱の協力,及びJSPS 科研費 JP18K19792 の助成を受けて行われたものである.

#### 【参考文献】

[1] 日野翔太,上見アレックス,升井義博, "遅延回路によって構成した非同期レジスタ回路を用いた逐次比較型 AD 変換器の低電圧・低消費電力化の検討,"電気学会論文誌C(電子・情報・システム部門誌),vol.139,no.1,pp.50-55,2019年1月.