# FPGA を用いた全結合イジングモデルの 並列更新の検討

## 南澤 晃<sup>†</sup> 河原 尊之<sup>†</sup> † 東京理科大学工学部電気工学科

### 1. はじめに

近年急速に進む IoT 社会においては、データを解析して最適化するシステムのハードウェアへの実装が進められている。本稿では、組み合わせ最適化問題の求解に有用なイジングモデルを FPGA に実装した。また、ハードウェア化の際の、並列処理によってスピンの並列更新を実装し、得られる解への影響を確認する。また、イジングモデルにおいて有用な並列更新数を検討することを目的として、並列更新数の変化による回路規模と計算速度を検討する。

## 2. 全結合イジングモデル

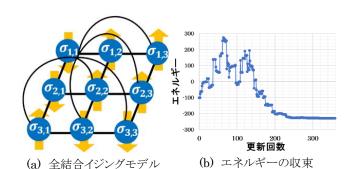

全結合イジングモデルとは、図 1(a)に示すような 2 値状態で表されるスピンの組み合わせで表現されるモデルであり、そのエネルギーはスピン間の相互作用Jと外場hを用いて(1)式で表される.

$$E = -\sum_{i} \sum_{k} \sum_{l} J_{i,j,k,l} \, \sigma_{i,j} \sigma_{k,l} - \sum_{i} \sum_{l} h_{i,j} \, \sigma_{i,j} \quad (1)$$

ここで、イジングモデルではエネルギーが最小となるスピン 状態へ遷移することから、(1)式の形でエネルギーが表現さ れる最適化問題として扱える。エネルギーを最小化するた めに、あるスピン $\sigma_{i,j}$ の向きはエネルギーが減少するように 更新するため、スピンの更新式は(2)式で求められる.[1]

$$\sigma_{x,y} = -sign(\Delta E_{xy} \pm T) \tag{2}$$

## 3. 並列更新の検討

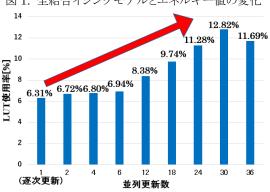

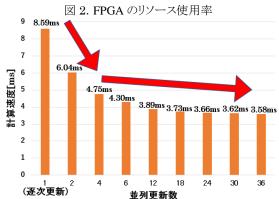

FPGA のようなハードウェアでは複数の処理を並列に実行可能なため、1 度の更新ステップで複数のスピンを並列更新することができる. 本稿では 6×6 スピンのイジングモデルにおいて、複数個のスピンの並列更新を実装して、回路規模と計算速度を検討する. 図 1 (b)に並列更新によるエネルギー値の遷移を示す. エネルギーはいずれの実装手法でも十分に低い値で収束を示し、SVMで最適解を求められることを確認した. 次に図 2 に FPGAリソースの使用率を示し、全更新終了までの計算時間を図 3 に示す. この結果から、並列更新数の増加に伴ってリソースの使用量は増加していくことがわかる. 一方、計算速度は逐次更新と比較して 2 倍以上の計算速度の向上が確認できたが、並列更新数の増加にしたがって計算時間の減少量は少なくなっていることがわかる.

#### 4. まとめ

本研究においては、イジングモデルは並列更新を用い

図 1. 全結合イジングモデルとエネルギー値の変化

図 3. イジングモデルの計算速度

ても適切な近似解を導出できることが確認できた.一方,並列更新数の増加によって計算速度は向上を示すが,回路規模の増加を考慮すると必要以上の並列更新には優位性がみられないということがわかった.また,6×6のイジングモデルでは6スピンの並列更新が最も効果的であることがわかった.今後の研究では,スピン数を増加させた場合や並列更新による解の精度の検証及び,更なる高速化と回路規模の縮小を目指した実装を行う予定である.

#### 参考文献

[1] K. Someya, et al., doi: 10.1109/NEWCAS.2016.7604797