# A Nanopower Full CMOS Sub-Bandgap Voltage Reference

Chang-Bum Park<sup>1</sup> and Shin-Il Lim<sup>2</sup>

<sup>1</sup> Department of Electronics and Computer Engineering, Seokyeong University 124, Seogyeong-ro, Seongbuk-gu, Seoul 02713, Korea Republic of <sup>2</sup> Department of Electronics Engineering, Seokyeong University 124, Seogyeong-ro, Seongbuk-gu, Seoul 02713, Korea Republic of E-mail: <sup>1</sup>wdrqq1@skuniv.ac.kr, <sup>2</sup>silim@skuniv.ac.kr

**Abstract:** This paper describes a sub-1V nanopower full CMOS bandgap reference (BGR) operated in subthreshold region. Complimentary to absolute temperature (CTAT) voltage generator was realized by using two n-MOSFET pair with body bias circuit to make a sufficient amount of CTAT voltage. Proportional to absolute temperature (PTAT) voltage was generated from differential amplifier by using different aspect ratio of input MOSFET pair. The circuits are implemented in 0.18um CMOS process. The simulation results show that the proposed sub-BGR generates a reference output voltage of 358mV, obtaining temperature coefficient of 32 ppm/C in -40°C to 120°C of temperature range. The circuits consume 43nW at 1V supply and operation range is 0.65 to 1.8V.

*Keywords--* Bandgap voltage reference, BGR, subthreshold, reference circuit, nanowatt

### 1. Introduction

As the development of Internet of Things (Iot) and wireless systems, the need for designing low voltage and low power bandgap voltage reference grows fast. As this trend, several bandgap reference (BGR) circuits have been released. The resistor-less voltage reference that operates in nano-watt power consumption with one bipolar transistor has been reported [1]. However, the bipolar transistor occupies larger area than MOSFET and needs an additional mask layer. A sub-1V full CMOS voltage reference circuit that is based on gate-source voltage of MOSFET to generate complementary to absolute temperature (CTAT) voltage is published [2]. However, the reference voltage changes significantly with process variations. Another BGR [3] uses body bias technique to reduce process variation and the proportional to absolute temperature (PTAT) voltage  $(\Delta Vgs)$  is generated by n-MOSFET pair with different oxide thickness. However, the circuit is very restrictive to apply on systems due to very low output reference voltage and also it needs a current trimming for further reducing the voltage change due to process variations. In this paper, to solve above problems, we present a new sub-1V full CMOS bandgap voltage reference which consumes few tens of nano-watt with very small variations among the significant variations of temperature, supply voltage and process.

This paper organized by follows: Section II presents the operational principle of CTAT voltage generator and PTAT voltage generator. Proposed sub-BGR circuits are described in section III. Section IV shows the simulation results of proposed BGR. Conclusions are given at section V.

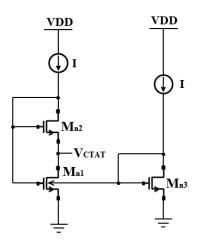

Mn1, Mn2, Mn3 : Sub threshold

Mn1, Mn3 : High Vth (High voltage MOSFET)

Mn2 : Low Vth (Low voltage MOSFET)

Fig. 1. Proposed CTAT voltage generator

### 2. Operation Principles

#### 2.1 CTAT voltage generator

In conventional BGR circuits, CTAT voltage is created by the base-emitter voltages (VBE) of bipolar junction transistors or the threshold voltages (Vth) of MOS transistors. However, VBE and Vth are variable parameters following process variations. Particularly, Vth largely changes depending on process variations. As the result, the variation of CTAT voltage will affect output reference voltage. In recent reported sub-BGR circuits [2] [6], the architecture as shown in Fig. 1 is usually adopted for generating a process invariant PTAT voltage. However, we modified the architecture to have CTAT behavior to apply to our overall circuit design as will be shown later. However, process variations partially remain in the circuit [7] since the threshold voltage of Mn1 (HVTMOS) and Mn2 (LVTMOS) change differently by process variations as will be shown later. Therefore, we adopted body bias circuit to reduce process variations caused by  $\Delta V th$ between Mn1 and Mn2. Fig. 1 shows proposed architecture of CTAT voltage generator. Mn1 is a high voltage MOS transistor and Mn2 is a low voltage MOS transistor. The calculation of VCTAT is shown below.

The subthreshold current for a drain-source voltage of MOSFET can be expressed as

$$I_{ds} = \mu C_{ox}(\eta-1) V_T^2 \left(\frac{W}{L}\right) exp\left(\frac{V_{gs} - V_{th}}{\eta V_{th}}\right) [1 - exp\left(-\frac{V_{ds}}{V_T}\right)]$$

(1)

Where  $\mu$ ,  $C_{ox}$ ,  $\eta$ ,  $V_T$ , W/L,  $V_{gs}$  and  $V_{th}$  represent carrier mobility, gate-oxide capacitance, subthreshold slope factor, thermal voltage, aspect ratio, gate-source voltage and threshold voltage respectively. When  $V_{ds} >> V_T$ , Eq. (1) can be deduced as

$$V_{gs} = V_{th} + \eta V_T \ln(\frac{I_{ds}}{\mu C_{ox}(\eta-1)V_T^2\left(\frac{W}{L}\right)})$$

(2)

Therefore,  $\Delta V_{gs}$  between  $M_{n1}$  and  $M_{n2}$  can be calculated by

$$\Delta V_{gs} = V_{CTAT} = V_{gs,Mn1} - V_{gs,Mn2}$$

$$= \left(V_{th,Mn1} - V_{th,Mn2}\right) + \eta V_T \ln \left(\frac{t_{ox,Mn2}(W_{/L})}{t_{ox,Mn1}(W_{/L})}\right)$$

(3)

Assuming the same size of both transistors and the difference of threshold voltage between the high voltage MOS transistor (M<sub>n1</sub>) and the low voltage MOS transistor  $(M_{n2})$ , and since the voltage of second term is much smaller than the voltage of first term, Eq. (3) can be reduced as

$$V_{\text{CTAT}} \approx \left( V_{\text{th},\text{Mn1}} - V_{\text{th},\text{Mn2}} \right) \tag{4}$$

Eq. (4) presents CTAT behavior since positive threshold voltage difference shows negative voltage coefficient. Furthermore, supposing the same  $\Delta V_{th}$  between  $M_{n1}$  and  $M_{n2}$  for each process corner, the variation of  $V_{CTAT}$  can be reduced even in the process variations

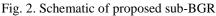

Fig. 3. PTAT voltage generator [5]

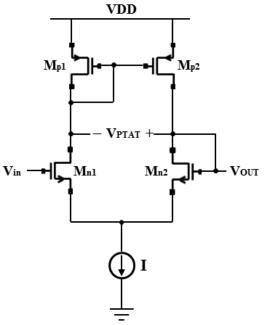

## 2. 2 PTAT voltage generator

Fig. 3 shows the PTAT voltage generator [5] which consists of a differential pair with a current mirror. The calculation of V<sub>PTAT</sub> can be expressed as

$$V_{\text{PTAT}} = V_{\text{in}} - V_{\text{out}}$$

$$= V_{\text{gs,Mn1}} - V_{\text{gsMn2}}$$

$$= V_{\text{th},\text{Mn1}} - \eta V_{\text{T}} \ln \left( \frac{I_{\text{ds},\text{Mn1}}}{I_0 K_{\text{Mn1}}} \right) - \left( V_{\text{th},\text{Mn2}} + \eta V_{\text{T}} \ln \left( \frac{I_{\text{ds},\text{Mn2}}}{I_0 K_{\text{Mn2}}} \right) \right)$$

(5)

Where I<sub>0</sub>, and K represent  $\mu C_{ox}(\eta-1)V_T^2$  and aspect ratio. Assuming the same V<sub>th</sub> and the same current of differential input transistor pair, Eq. (5) can be simplified as

$$V_{\text{PTAT}} = \eta V_{\text{T}} \ln \left( \frac{\kappa_{\text{Mn1}} \kappa_{\text{Mp1}}}{\kappa_{\text{Mn2}} \kappa_{\text{Mp2}}} \right) \approx \eta V_{\text{T}} \ln \left( \frac{\kappa_{\text{Mn1}}}{\kappa_{\text{Mn2}}} \right)$$

(6)

Therefore, PTAT voltage can be generated by setting  $K_{Mn1}/K_{Mn2}>1.$

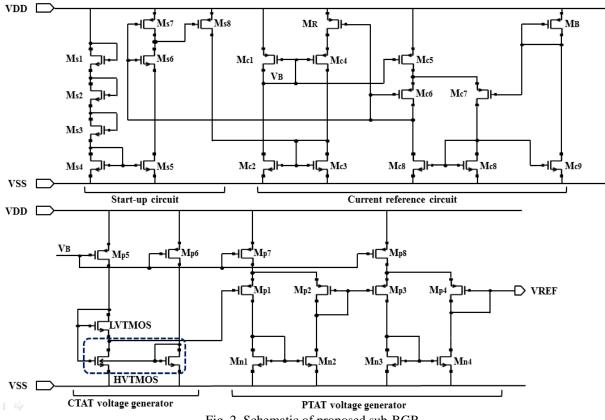

#### 3. Proposed BGR Circuits

Fig. 2 shows a schematic diagram of proposed sub-BGR. The current reference circuit [4] generates about 10 nA current and supplies it to the other parts of circuits. All MOSFETs are operated in subthreshold region except for MOS resistors (M<sub>R</sub>, M<sub>B</sub>) which are operated in the deep triode region. The currents flow through M<sub>R</sub> and M<sub>B</sub> are equal duo to the same aspect ratio. And the generated currents are robust to process variation because M<sub>R</sub> and M<sub>B</sub> are biased from the gate-source voltage of M<sub>B</sub> and have the same threshold voltages. The CTAT voltage generator with body bias circuit to the body of Mn1 makes process invariant CTAT voltage. This CTAT voltage was connected to an input MOS transistor (Vin) of PTAT voltage generator. The two-stage PTAT voltage generator was designed to create the sufficient amount of PTAT voltage. Thus the temperature invariant output reference voltage can be generated.

#### 4. Simulation Results

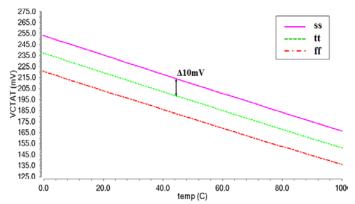

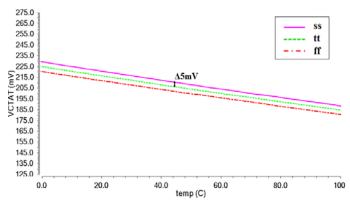

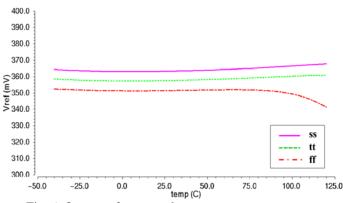

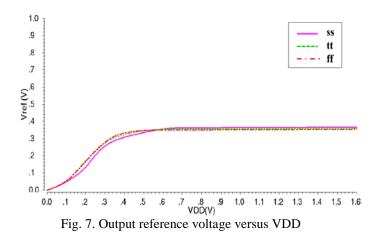

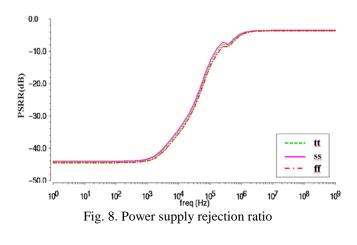

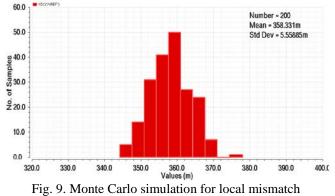

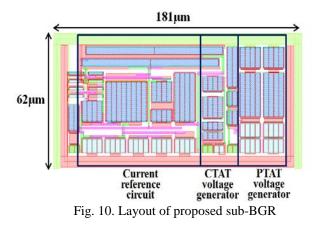

Simulations were performed with 0.18-um CMOS technology from a 1-V supply voltage. Fig. 4 and Fig. 5 show simulated CTAT voltage temperature behavior from the CTAT voltage generator according to the body bias circuit. The simulated values of  $\Delta V_{\text{CTAT}}$  are 10mV and 5mV for each process corner respectively. The output reference voltage as a function of temperature is shown in Fig. 6. Simulation results show the small process variation of 5.4mV (1.508%) at each process corner. And 31ppm/°C, 41ppm/°C and 70ppm/°C on TT(typical-typical), SS(slowslow) and FF(fast-fast) are resulted in the temperature range of -40°C to 120°C respectively. Fig. 7 shows the simulation results of proposed sub-BGR. The output reference voltage of 358mV is achieves in the supply voltage range from 0.65V to 1.6V. The simulated results of PSRR are 44dB at 100Hz for each process corner as shown in Fig. 8. To determine local mismatch effects, Monte Carlo simulation was performed as shown in Fig. 9 ( $\sigma/\mu=1.54\%$ ). The power dissipation at 0.65V supply voltage was 23nW. Fig. 10 shows the layout result.

Fig. 4. CTAT voltage versus temperature w/o body bias

Fig. 5. CTAT voltage versus temperature w/ body bias

Fig. 6. Output reference voltage versus temperature

## 5. Conclusion

Sub-1V BGR without BJTs and resisters is introduced. Two N-MOSFET pair with body bias circuit makes a sufficient amount of CTAT voltage. Differential amplifier configuration by determining different aspect ratio of input MOSFET pair generates PTAT voltage. And the circuits are robust from process variations by using the process invariant CTAT voltage. The simulation results demonstrated that the sub-BGR circuit could generate the output reference voltage of 358mV and the power dissipation at the room temperature was 23nW at 0.65-V supply voltage.

#### Aknownledgement

This research was supported by the Industrial Core Technology Development Program (10049009) funded by the Ministry of Trade, Industry & Energy(MITIE), Korea and also supported by the MSIP (Ministry of Science, ICT and Future Planning), Korea, under the ITRC (Information Technology Research Center) support program (IITP-2016-H8501-16-1010) supervised by the IITP(Institute for Information & Communications Technology Promotion). The CAD tools were supported by IC Design Education Center (IDEC).

#### References

- [1] Y. Osaki, T. Hirose and et al, "1.2-V supply, 100-nW

1.09-V bandgap and 0.7-V supply, 52.5-nW, 0.55-V

subbandgap reference circuit for nanowatt CMOS LSIs" *Sollid-State Circuits, IEEE Journal of* 48.6(2013): 1530-1538

- [2] Iman Fakharyan, Mehdi Ehsanian "A Sub-1V Nanowatt CMOS Bandgap Voltage Reference with Temperature Coefficient of 13ppm/C". 23rd Iranian Conference on Electrical Engineering, 2015

- [3] Yutao Wang, Zhangming Zhu, "A 0.45-V, 14.6-nW

CMOS Subthreshold Voltage Reference With No

Resistors and No BJTs," *Circuits And Systems, IEEE Transactions On*, Vol 62, No. 7, Jul. 2015.

- [4] T.Hirose, Y. Osaki, N. Kuroki, and M. Numa, "A nanoampere current reference circuit and its temperature dependence control by using temperature characteristics of carrier mobilities," in Proc. Eur. *Solid-State Circuits Conf.*, 2010, pp. 114-117.

- [5] A.-J. Annema, "Low-Power bandgap references featuring DTMOST's," *IEEE J.Solid-State Circuits*, vol. 32, no.7, pp.949-955, Jul. 1999.

- [6] H. Ma, F. Zhou, "A sub-1V 115nA 0.35µm CMOS voltage reference for ultra low-power applications", ASICON '09. *IEEE 8th International Conference on*, pp. 1074-1077, 2009

- [7] A. A, M. S. Baghini, "A Sub-1V 32nA Process, Voltage and Temperature Invariant Voltage Reference Circuit", VLSI Design and 2013 12th International Conference on Embedded Systems (VLSID), 2013 26th International Conference on, pp. 136-141, 2013.