# Pulse responses of a printed circuit board with a via and a bump

Daisuke Kobayashi\*, Shinichi Furukawa\*\*, and Takashi Hinata\*

\*College of Science and Technology, Nihon University

1-8-14, Kanda-Surugadai, Chiyoda-ku, Tokyo, 101-8308

E-Mail: kobayashi-d@sano-c.ac.jp

\*\*Sano College

973, Takahagicho, Sano-shi, Tochigi, 327-0821

#### 1. Introduction

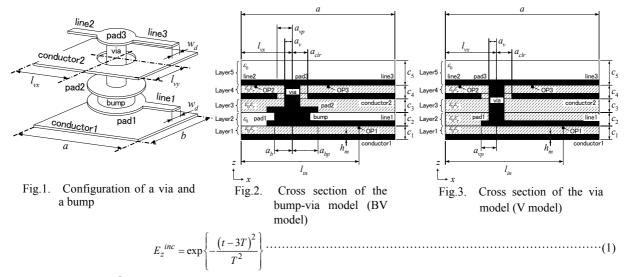

In this paper, pulse propagation characteristics are investigated for the fundamental multi-layered printed circuit model with a via and a bump as shown in Fig.1. The via is connected to the circular pads of conductor (labeled pad 2 and pad 3 in Fig.1) through the hole of conductor 1. The bump is put between pad 1 and pad 2. Pad 1 is connected to the transmission line labeled line 1.

Numerical results for pulse propagation are compared a bump-via connected structures with a via connected structures without a bump. The finite-difference time-domain (FDTD) method <sup>[1][2]</sup> has been successfully used for the analysis of our problem. FDTD method can analyze the pulse propagation characteristics as the boundary value problem for Maxwell equations. Numerical simulation can provide quantitative and accurate results which are difficult to measure directly.

## 2. Analysis

- 2.1 Analysis models The coordinate system and the structures of a multi-layered printed circuit board with a bump and a via are shown in Figs.1,2, and 3. Fig.2 shows the cross section on x-z plane of the bump-via model (BV model) whose striplines separated by dielectric layers are connected by both a via and a bump. BV model is a fundamental model throughout this paper and a part of structure in the practical PCB taken as BV model. BV model is consisted of five layered structures of three dimensions. Layer 1, layer 3, and layer 4 are dielectric substrates of the relative permittivity  $\varepsilon_r$  =3.4. Layer 2 and layer 5 are the air ( $\varepsilon_r$  =1.0). The detail of striplines, pads, and conductors placed into each layer are as follows.

- (1) Layer 1: The layer is composed of a dielectric sheet on the conductor 1. The stripline (line 1) of width  $w_d$  and the pad (pad 1) of radius  $a_{bp}$  are put on the dielectric sheet.

- (2) Layer 3: The layer which is put on a bump is composed of a dielectric sheet of thickness  $c_3$ . The conductor 2 with a through hole is out on the sheet.

- (3) Layer 4: The layer is a dielectric sheet on which the line2, pad3 and line3 are put. A via perpendicularly passes through the layer.

The conductor (conductor 2) with the clearance hole of radius  $a_{clr}$  is placed between layer 3 and layer 4. Pad 1 and pad 2 are connected by the bump of radius  $a_b$ , and pad 2 and pad 3 are connected by the via passing through a clearance hole of conductor 2.

Fig.3 shows the cross section on x-z plane for the via model (V model) whose striplines separated by dielectric layers are connected by only a via. V model is the structure prepared in order to discuss the influence to pulse response due to the bump of BV model. Pad 2 and the bump are removed and pad 1 and pad 3 of radius  $a_{vp}$  are directly connected by the via. The relative permittivity of layer 2 is  $\varepsilon_r$  =3 4

In Figs.1,2, and 3, line  $1 \sim \text{line } 3$ , pad  $1 \sim \text{pad } 3$ , conductor 1, conductor 2, a via, and a bump are the perfect conductor of thickness  $h_m$ . All dielectric sheets are lossless.

2.2 Analysis method A transient analysis of a pulse propagation for BV model and V model is computed by FDTD method<sup>[1][2]</sup>. The cell size  $\Delta$  is defined as  $\Delta = \Delta x = \Delta y = \Delta z$ . The time step  $\Delta t$  is determined so as to satisfy the stability condition of Courant <sup>[9]</sup>. Ten layered PML<sup>[1]</sup> is imposed as the absorbing boundary condition around the each model. An incident excitation pulse is a Gaussian pulse defined as:

where T=0.5ps.  $E_z^{inc}$  is uniformly excited under line 1 at  $x=l_{in}$  in Figs.2 and 3.

#### 3. Numerical results

The sizes of BV model and V model in Figs.2 and 3 are denoted in Table.1. These data are practical values which are used for the printed circuit board<sup>[3]</sup>. We set three observation points (OP1, OP2, and OP3 in Figs.2 and 3) for clarifying the status of pulse propagating from line 1 to line 2 and line 3. OP1 (at  $x=250[\mu m]$  and  $y=70[\mu m]$ ) is just under line 1. OP2 (at  $x=25[\mu m]$  and  $y=70[\mu m]$ ) is just under line 2 and line 3, respectively. The distance from OP2 to the center of the via is same as that from OP3 to the center of the via.

Table 1. The size of each part of the analysis model [μm]

| a=300              | c <sub>5</sub> =30         | $l_{vx} = 100$ |

|--------------------|----------------------------|----------------|

| b=140              | $a_v = 15$                 | $l_{vy} = 70$  |

| c <sub>1</sub> =25 | $a_{vp} = 30$              | $h_m=10$       |

| c <sub>2</sub> =25 | $a_b = 35$                 | $l_{in} = 250$ |

| c <sub>3</sub> =25 | <i>a</i> <sub>bp</sub> =50 | $w_d = 20$     |

| c <sub>4</sub> =25 | $a_{clr}$ =30,40,50        |                |

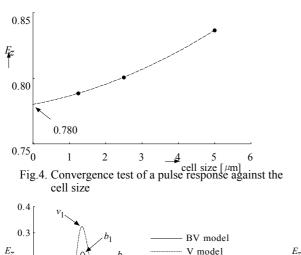

Fig.4 shows a convergence test of the amplitude of  $E_z$  against the cell size  $\Delta$  of FDTD on OP1 for BV model. From Fig.2, it is found that the relative error to the extrapolated true value of the amplitude of  $E_z$  can be kept less than 5% by taking  $\Delta$ in the range of  $\Delta \le 2.5$  [µm]. In the following numerical analysis, the relative error of the amplitude of  $E_z$  is always kept below 5% by selecting  $\Delta$  carefully.

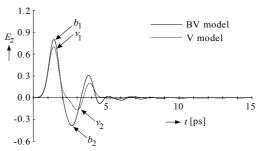

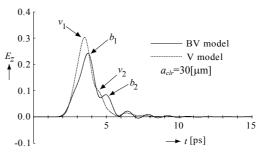

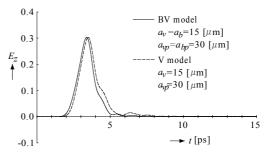

Fig.5 shows pulse responses observed on OP1. The results of the BV model and V model are indicated by the solid line and the broken line, respectively.  $b_i$  (as labels of BV model) and  $v_i$  (as labels of V model) at the response waveforms are utilized as a help of the considerations throughout numerical results. In Fig.5,  $b_1$  and  $v_1$  are the excited pulse.  $b_1$  has a larger peak value of response than the peek value of  $v_1$ . This is because the permittivity of each model in layer2 is different.  $b_2$  and  $v_2$  are the reflection waves from a bumps and/or a via. The response after  $b_2$  and  $v_2$  is continued decreasing by a multiple reflection generating in the substrate.

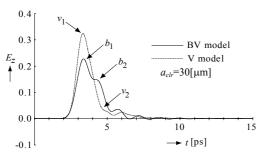

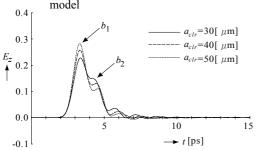

Fig.6 shows pulse responses observed on OP2. In the case of V model,  $v_2$  due to the influence of multiple reflection is continued after  $v_1$  which the excited pulse is arrived on OP2 by propagating through the via. BV model also has a similar response. However, a large distortion of waveform is observed for BV model, thus having a complicated structure with a bump.

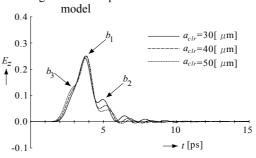

Fig. 7 shows pulse responses observed on OP3. In the case of BV model,  $b_1$  at OP3 is larger than that of OP2, and  $b_2$  at OP3 is smaller than that at OP2. In the case of V model. Whereas the response time at the peak value of  $b_1$  and  $v_1$  at OP2 is same, the peak value of  $b_1$  for OP3 is later than that of  $v_1$ .

In Figs.5,6 and 7, a clearance hole of radius  $a_{clr}$  which is made into conductor 2 had been fixed at  $a_{clr}$ =30[ $\mu$ m].

To compare with the responses in Figs.6 and 7 we computed the responses when  $a_{clr}$  is  $30[\mu m]$ ,  $40[\mu m]$ , and  $50[\mu m]$ .

For BV model, Figs. 8 and 9 show pulse responses observed at OP2 and OP3, respectively. The

Fig.5. Pulse responses at OP1 for BV model and V model

Fig.6. Pulse responses at OP2 for BV model and V

Fig.7. Pulse responses at OP3 for BV model and V model

Fig.8. Pulse responses at OP2 for BV model when varying a clearance hole radius  $a_{clr}$

Fig.9. Pulse responses at OP3 for BV model when varying a clearance hole radius  $a_{clr}$

following results are found from the figures.

- (1)  $b_1$  at OP2 increases as  $a_{clr}$  is increased, on the other hand  $b_1$  at OP3 does not change.

- (2) When  $a_{clr}$  is changed from 30[ $\mu$ m] to 50[ $\mu$ m], the modification at  $b_1$  on OP3 is smaller than that

- (3) For OP3,  $b_2$  decreases as  $a_{clr}$  is increased.

- (4) The rise of response on OP2 is not almost influenced by the size of  $a_{clr}$ .

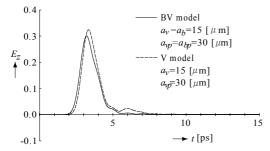

When the pulse excited from OP1 was arrived to OP2 or OP3, the large pulse distortion was observed in BV model,. If the clearance hole radius was set up larger, the pulse distortions at OP2 were improved. This means that less distortion of the pulse responses on OP2 and OP3 is trade-off for the size of the clearance hole. From these results, it is necessary to find out fundamental causes of the pulse distortion arising in BV model. We discuss the influence of the bump which is put between pad 1 and pad 2. The bump radius is  $a_b$  and the radiuses of pad 1 and pad 2 are equally  $a_{bp}$ . When radius  $a_{bp}$  of pad 1 and pad 2 is reduced from  $a_{bp}$ =50[µm] (original size in Table.1) to  $a_b$ =30[µm] (same size as the via pad (pad 3) with radius  $a_{vp}$ ), pulse responses at OP2 and OP3 are shown by solid lines ( $a_{bp}$ = $a_{vp}$ ) in Figs.10 and 11, respectively. The responses of V model in Figs.6 and 7 are also indicated by broken lines ( $a_b \neq a_v$ ). The rise time in BV model becomes slightly earlier than that in V model. The large pulse distortion in BV model is not almost observed. As a result, it is concluded that the pulse distortion on OP2 and OP3 is depended on the radius of the pads added to the bump. From above results, it is found that the pulse distortion on a stripline after propagating the bump part can be minimized if the bump pad radius can be small (as much as the via pad radius) by designing the bump radius as small as possible.

Fig.10. A comparison of a pulse response (solid line) of BV model and a pulse response (broken line) of V model at OP2.  $a_b$  and  $a_{bp}$  of BV model is set up similarly to  $a_v$  and  $a_{vp}$  of V model, respectively

Fig.11. A comparison of a pulse response (solid line) of BV model and a pulse response (broken line) of V model at OP3.  $a_b$  and  $a_{bp}$  of BV model is set up similarly to  $a_v$  and  $a_{vp}$  of V model, respectively

### 4. Conclusions

In this paper, pulse propagation characteristics in multi-layered PCB with a via and a bump were investigated. We proposed BV model (with a via and a bumps) and V model (with a via). V model was prepared as a comparison model to discuss the influence of a bump. The main results are as follows.

- (1) The pulse responses for BV model are distorted comparing with those for V model.

- (2) In BV model, although the radius  $a_{clr}$  of a clearance hole located into conductor plate can be controlled (in the range of  $30[\mu m] \le a_{clr} \le 50[\mu m]$ ), an improvement effect to a pulse response is trade-off by the propagation direction of pulse.

- (3) It is found for BV model that the pulse distortion on a stripline after propagating the bump can be minimized if the bump pad radius is nearly equal to the via pad radius.

#### References

- [1] T.Uno, "Finite Difference Time Domain Method for Electromagnetic Field and Antennas," Corona Publishing,1998

- [2] K.S.Yee, "Numerical Solution of Initial Boundary Value Problems Involving Maxwell's Equations in Isotropic Media," IEEE Transactions on Antennas and Propagation, Vol. AP-14, No.3, pp. 302-307, May, 1966.

- [3] H.Kato, S.Akimoto, T.Okuma, and, R.Iino, and T. Tsukamoto, "Development of Multi Layers Tape-BGA Substrate," Proceedings of International Conference on Electronics Packaging, p358-363, 2002.

- [4] B.J.LaMeres and T.S.Kalkur, "Time Domain Analysis of a Printed Circuit Board VIA," Microwave Journal, pp.76-82, Nov., 2000.

- [5] Q.Gu, Y.E.Yang, and M.A.Tassoudji, "Modeling and Analysis of Via in Multilayered Circuits," IEEE Trans. Microwave Theory Tech., vol. MTT-41, No.2, pp.206-214, Feb., 1993.

- [6] T.Nakamura, T.Hamada, T.Okubo, and T.Ishii, "Deveropment of High Density Build-up Substrates by Via Filling," Technical report on IEICE, EMD2000-76, pp.13-16, 2000.

- [7] D.Kobayashi, S.Furukawa, and T.Hinata, "FDTD Analysis of Printed Circuit Board with Via," EMT-02-118, pp.19-24, October, 2002

- [8] M.Ikenaga and K.Kato, "Developing Trend of High Pin Count BGA," Journal of Japan Institute of Electronics Packaging, Vol.5, No.5, pp.406-409, 1998.