# ADAPTIVE DIGITAL PREDISTORTION USING THE FPGA ELECTRONIC ARCHITECTURE

Marcos Paulo de Souza Silva, Adriano de Andrade Mello $^{(\Delta)}$ , Fabio Garcia Pina $^{(\Delta)}$  Leonardo de Souza Ribeiro, José de Souza Lima $^{(\Delta)}$ , Maurício Silveira National Institute of Telecommunication – INATEL

National Institute of Telecommunication – INATEL

João de Camargo Avenue 510, Phone: +55 35 3471-9332

P.O. Box: 05, Web Page: <a href="http://www.inatel.br">http://www.inatel.br</a>

37540-000, Santa Rita do Sapucaí, MG, Brazil

\*\*Comparison of Comparison of Compariso

**ABSTRACT** – Digital pre-distortion is an efficient means of compensating that can be help many engineering designers to control the power amplifiers non-linearity, using the *FPGA* electronic architectures as well as the adaptive *Look Up Table* implementation. Actually, many efforts of research have been done with the essential purpose to insert an efficient numerical algorithm in the hardware development. The main objective of this paper is to present a new way of how to develop algorithms using the numerical methods with the aid of the linear correlation as well as a linear regression. Thus, will turns out in a very great progress in the technique adopted applied to the adaptive pre-distortion linearization.

Index terms - Digital Pre-Distortion, Linearization, FPGA Architecture, Numerical Methods

# 1. INTRODUCTION

The adaptive pre-distortion of the modulated signals is a technique used to compensate distortions provoked by power amplifiers. Recently, many researcher centers have been using this technique due to the fact that it constitutes an efficient approach for a large class of *RF* models to control the intrinsic problems related with the non-linearity that appear in the implementation of many telecommunications systems. This technique has as one of its main fundamental principles to apply a distortion over the input signal with contrary effect to that one provoked by the amplifier, in order to obtain a linear answer of the system. As an additional convenience we can see an expressive reduction of the intermodulation products as well as the harmonic distortions that appear inside the band of the signal intrinsically.

Another alternative solution that we can set at the moment of the hardware implementation should be the reduction of the input power of the amplifier, in order to adjust the normal operation of the device over the linear region. Nowadays, this technique not have been using extensively just because it does not permit to explore all the potentially of the power amplifier, and it has a great consequence with respect to the cost of the transmission system [1] - [7].

#### 2. PROGRAMMABLE LOGIC DEVICE

The electronic hardware we will present in this paper can be implement by using architectures like: *Programmable Logic Device* (*PLD*), which is a digital logic circuit that permits to implement a configuration including the *Programmable Logic Array* (*PAL*), *Field Programmable Gate Array* (*FPGA*) and the *Complex Programmable Logic Device* (*CPLD*).

In our specific case we set the option to work with the FPGA structure since that this component has may convenience like: a very low cost, an easy programming and it demands a very simple manipulation. Besides of that, we can modify our project in any time without the necessity of to change the *chip*, which turns out in a very flexible component if we compare it with Application Specific Integrated Circuit (ASIC). Also we need to take into account that this device has an internal composition composed for segmented slide bars with metal composition, which crosses the chip in both vertical and horizontal directions and permit all connection in many alternative forms in accordance with all demanded requirements imposed over the project.

### 3. APPROACH DIGITAL PREDISTORTER

A very high efficiency and an expressive linearity are demanded when we are working with power amplifiers for TV signals. Due to the non-linear characteristics of these equipments we will make the use of linearization circuits by adopting the digital pre-distortion technique implemented using the as FPGA's electronic architecture. Our project of the linearizator circuit will follow models, studied and research in accordance with [8] - [12].

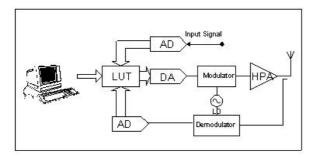

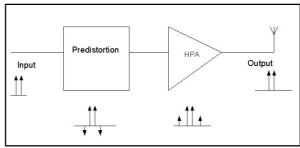

Inside of the FPGA structure beyond the slide bars, it possess some *LUT*'s that can store the information to be transmitted, they permit to compare the transmitted signal with the feedback one and after that the data can be up to date at the *LUT*. If we taking into account both comparison and update approaches we can call the final hardware implementation an adaptive circuit, and in this case the best results have been gotten when we analyze the interrmodulation products of 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> orders. Fig. 1(a) illustrates the block diagram of the implemented hardware, while the Fig. 1(b) depicts that one corresponding to the pre-distortion circuit.

Figure 1(a) – Hardware Implementation.

Figure 1(b) – Digital Pre-distortion Block Diagram.

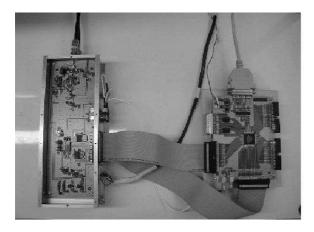

Figure 2(a) – Digital Pre-distortion Hardware.

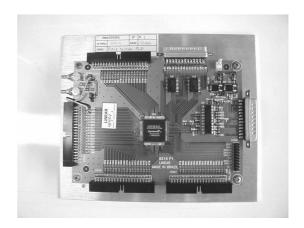

Figure 2(b) - MLP using the *FPGA*.

Our main proposal is to record in the *FPGA* a transference function contrary to that one generated by the power amplifier, and the imposition that we must to work with TV signals on real time demands that the correction must be very fast and with an adaptive process such that the user final does not perceive the intermediate operations. Fig. 2(a) presents a *Programmable Logic Module (MLP)* and the electronic implementation with both *AD* and DA converters, while in the Fig. 2(b) we only visualize the *MLP*.

# 4 - EXPERIMENTAL RESULTS THE LABORATORY

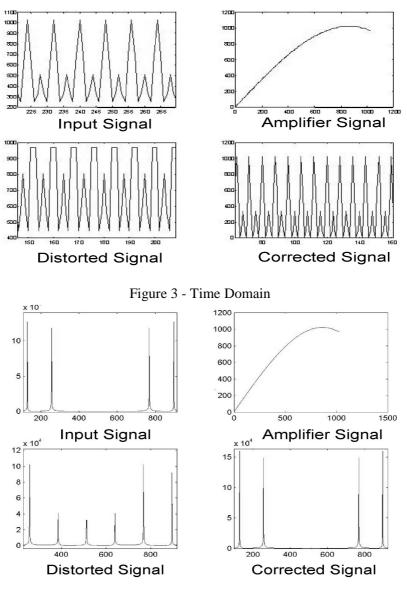

The results gotten with this hardware implementation are satisfactory and very important in the future system improvements, and it is easy to check that we correct the signal and it is possible to stay very close to that original one. The Figure 3 represent both input, amplifier, distorted and corrected signals in the time domain, while the Figure 4 illustrate the same signals in the frequency domain unless the amplifier signal that is in the time domain, as a comparison.

Figure 4 – Frequency Domain

These mentioned graphs had been made with the aid of the *MatLab* numerical platform, where after the simulation all data are recorded in the *FPGA*. Some classic laboratory instrument are used, like: oscilloscope, spectrum analyzer, etc. and we have gotten accurately the same curves that we have been simulated.

The input signal is a curve composed by two frequencies and after to pass for the amplifier, which has intrinsically no ideal performance the signal will distorted with the generation of harmonic components in the frequency domain and in consequence occurs some changes in its format in the time domain. By utilizing numerical methods over themselves it is possible to reestablish the original form of the input signal, which validates the linearization process we have adopted in this research and our developed technique [13] – [16].

#### 4. CONCLUSION

This research permits to us to conclude that all laboratory activities have a great importance in the national marketing of broadcasting and indicates that is possible to increase the power efficiency of the system, making possible the reduction costs of the equipments. In addition, we can visualize more viable the digital TV signal transmission, independently of the pattern standard that each country will be adopt. The demanded requirements with respect to the power reduction and an expressive increase in the mistake tax provoked by the lack of linearity of the power amplifiers can be accomplished it we use the FPGA's architectures that permit a easy way to set the numerical programming.

#### REFERENCES

- [1] Vuolevi, J., and Rahkonen, T., Distortion in RF Power Amplifiers; Norwood: Artech House, 2003.

- [2] Vuolevi, J., Analysis, measurement and cancellation of the bandwidth and amplitude dependence of intermodulation distortion in RF power amplifiers; Department of Electrical Engineering, University of Oulo, 2001.

- [3] Maas, S.A., Nonlinear Microwave Circuits, IEEE Press, Piscataway, NJ, USA, 1988.

- [4] Cripps, S.C., Advanced Techniques in RF Power Amplifier Design, Artech House, 2002.

- [5] Cripps, S.C., RF Amplifiers for Wireless Communications; Norwood: Artech House, 1999.

- [6] Kenington, P.B., High-Linearity RF Amplifier Design; Artech House, Norwood, MA, USA, 2000.

- [7] Pothecary, N., Feedforward Linear Power Amplifiers; Norwood: Artech House, 1999.

- [8] Mello, A.A., Rodrigues, H.D., Lima, J.S, Silva, M.P.S., Silveira, M., *A New Numerical Approach in the Linear Analysis of RF Amplifiers*, IEEE, MTT-S 2003 33<sup>rd</sup> European Microwave Conference, Munich, GE.

- [9] \_\_\_\_\_, Adaptive Digital Predistortion To Reduce the Power Amplifier Nonlinearity, IEEE APS-URSI 2003, Columbus, Ohio, USA.

- [10] \_\_\_\_\_, Uma Eficiente Abordagem Numérica para a Linearização de Amplificadores de Potência; submitted Revista Eletrônica do IEEE Section 09.

- [11] Mello, A.A., Rodrigues, H.D., Lima, J.S., Silveira, M., Pereira, W.N., Ribeiro, J.A.J., *Transmitter Linearization using Digital Pre-distortion*, IEEE APS-URSI 2002, San Antonio, Texas, USA.

- [12] Mello, A.A., Rodrigues, H.D., Lima, J.S., Silva, M.P.S., Silveira, M., Pereira, W.N., *O uso da técnica de pré-distorção digital na linearização de amplificadores de potência em RF*, International Week of Telecommunication 2002, Santa Rita do Sapucaí, *INATEL*, BRAZIL.

- [13] Mello, A.A., Pina, F.G., Ribeiro, L.S., Silva, M.P.S., Lima, J.S., Silveira, M., *Adaptive Linearization Digital Signals: I and Q*; to be presented IEEE APS-URSI 2004, Monterey, CA, USA.

- [14] Lima, J.S., *Linearization of TV Transmitters with IF Pre-distortion*, Telecommunication Journal, INATEL, BRAZIL, 1998.

- [15] \_\_\_\_\_\_, *Medidas de desempenho em Sistemas 8-VSB e COFDM*, International Week of Telecommunication 2002, Santa Rita do Sapucaí, INATEL, BRAZIL.

- [16] Lima, J.S., Silva, M.P.S., Silveira, M., Campos, M.V., An efficient analysis of the performance of nonlinear devices using as a tool the Software ADS, to be presented IEEE WCETE 2004 World Congress on Engineering and Technology Education, Guarujá, Brazil.