# HIGH FREQUENCY PROPERTIES OF GaN BASED TRANSISTORS FOR MICROWAVE AND RF CONTROL APPLICATIONS

Nikolai DROZDOVSKI and Robert H. CAVERLY

Department of Electrical and Computer Engineering, Villanova University

800 Lancaster Avenue, Villanova, PA 19085 USA

E-mail: caverly@ece.vill.edu

#### Abstract

High frequency properties of AlGaN/GaN heterostructures field-effect transistors (HFET) used as control components for high-power microwave and RF control devices have been studied. A modified linear operation model was developed for these components so that electrical parameters may be determined as a function of frequency in better agreement with the experimental data. A model has been developed for the single shunt connected switch. From the model, it was established that the on-state low resistance and capacitance of the GaN switching HFET are frequency dependent. This phenomenon can have a dramatic impact on the control capabilities and design of microwave and RF control circuits using these devices. The modification of the two-terminal HFET model was implemented to compute the frequency dependence of the transistor impedance. Details of this modified GaN HFET switching model as well as simulation and measurement results are in this paper.

### 1. Introduction

Recent advances in semiconductor technologies based on wide bandgap materials such as GaN promise to extend the power level of FET-based microwave circuits by at least a factor of five due to their higher breakdown voltages [1-2]. The study of one of these structures, the HFET, for microwave and RF power control purposes is especially important because of their use in small size, high-density front end applications or in multifunction systems.

The low-power impedance frequency properties of field-effect transistors based on AlGaN/GaN heterostructure are studied. The first small-signal GaN HFET equivalent circuit studied [3-5] showed the impedance properties versus DC gate voltage control and transistor geometry, showing the relationship between gate length  $L_{\rm g}$  and channel length  $L_{\rm ch}$  for  $L_{\rm g}$  less than  $L_{\rm ch}$ . The second version of that model [5] described the impedance properties of transistors with shorter gate length compare with the channel length:  $L_{\rm g}$  much less  $L_{\rm ch}$ . These earlier model versions, however, do not adequately reflect the high frequency properties of the transistors that have been experimentally observed under low-power and high-power condition. The modified equivalent circuit is introduced in the paper and shows reasonable agreement with experimental data.

# 2. Distributed equivalent circuit

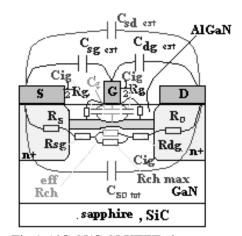

Figure 1 shows the structure of the AlGaN/GaN heterojunction field-effect transistor with the main network of resistors and capacitors forming the small-signal equivalent circuit. The two-dimensional electron gas (2DEG) located at the heterointerface is controllable only by the gate voltage of the device. Red marked elements of the network appear in the off-state, whereas the green elements only in the on-state, and the blue elements are present in both transistor states.

The source-drain resistance model corresponding to this network shows two  $n^+$  regions under the source or drain and three regions in the heterointerface: directly under the gate and between gate-source and gate-drain. The value of the source and drain region resistors for the symmetrical transistor may be written as:

Fig.1 AlGaN/GaN HFET elements network

$$R_{s} = R_{d} = \frac{1}{\mu_{n} N \ q} \times \frac{L_{s(d)}}{W h_{n^{+}}},\tag{1}$$

where  $\mu_n$  is the low-field mobility, N is bulk impurity concentration in  $n^+$  region, q is the electronic charge, W is the gate width of the HFET,  $h_{n^+}$  is  $n^+$  region depth, and  $L_{s(d)}$  is the source (or drain) length. The 2DEG governs the resistance in the conductive channel, hence, the channel resistance may be written as:

$$R_{ch} = R_{sg} + R_{ch}^{eff*} + R_{dg} , \qquad (2)$$

where  $R_{sg}$  and  $R_{sd}$  are the 2DEG source-gate and gate-drain resistance, and  $R_{ch}^{eff}$  is the channel resistance under the gate where the 2DEG sheet density is under direct DC gate voltage  $V_g$  control. The effective length  $L_{ch}^{eff}$  of this central part of the channel is:

$$L_{ch}^{eff} = (1 + \lambda_1) L_{g}, \qquad (3)$$

where  $L_g$  is the gate length and  $\lambda_1$  is a characteristic fitting coefficient taking into account the spreading of the DC electric field around the gate ( $\lambda_1$  is typically between 0.05 and 0.25).

For a symmetrical transistor and zero voltage between source and drain ( $V_{sd} \approx 0$ ) the source-gate or gate-drain resistances may be written as:

$$R_{sg} = R_{dg} = \frac{\left(L_{ch} - L_{ch}^{eff}\right)/2}{W} \times \frac{1}{q\mu_n n_s^{V_g = 0}},$$

(4)

where  $L_{ch}$  is the channel length (i.e. distanse between source and drain regions), and  $n_s^{V_g=0}$  is the 2DEG sheet density under zero gate voltage condition and it is independent on the DC control gate voltage. The resistance corresponding to the area directly under the gate can be shown to be:

$$R_{ch}^{eff*} = \frac{R_{ch}^{eff}}{\left(1 + \left(R_{ch}^{eff} / R_{ch \max}\right)^{\gamma_2}\right)^{1/\gamma_2}},$$

(5)

where

$$R_{ch}^{\it eff} = \frac{L_{ch}^{\it eff}}{W} \times \frac{1}{q\mu_{n}n_{s}(V_{g})}$$

,  $R_{ch\,\,\rm max} = \frac{1}{q\mu_{\it GaN}N_{\it GaN}} \times \frac{L_{\it g\,\,eff}}{Wh_{\it GaN}}$ ,  $R_{ch}^{\it eff}$  is the 2DEG resistance under the

gate,  $n_s(V_g)$  is the gate voltage dependent 2DEG sheet density,  $R_{ch\ max}$  is related to the bulk GaN resistivity under the gate region,  $h_{GaN}$  is the GaN thickness,  $N_{GaN}$  is the impurity level, and  $\mu_{GaN}$  is the mobility in GaN. The parameter  $\gamma_2$  is a characteristic parameter for the transition to reach the  $R_{ch\ max}$  values and reflects the interaction between the bulk semiconductor and the quantum nature of the 2DEG.  $\gamma_2$  was found to be approximately 0.3 [3]. Resistance  $R_g$  represents the resistance of the bulk AlGaN between the 2DEG layer and the gate. For a given HFET geometry, the depletion layer  $w_j$  caused by the gate Schottky barier exceeds the AlGaN layer thickness even for  $V_g = 0$ . We can estimate the resistor value as:

$$\begin{bmatrix} R_g = R_{g \text{ max}} & \approx & 1...10 \text{ MOhm}, & \text{for } w_j \ge d_i \\ R_g = \frac{w_j}{d_i} \times R_{g \text{ max}} + \frac{1 - w_j}{d_i} \times R_{g \text{ min}}, & \text{for } 0 < w_j < d_i, \\ R_g = R_{g \text{ min}} = \frac{L_{g \text{ eff}}}{W} \times \frac{1}{\mu_{AlGaN} N_D q}, & \text{for } w_j = 0 \end{bmatrix}$$

$$(6)$$

where  $N_d$  is impurity level,  $\mu_{AlGaN}$  is the mobility in AlGaN (in the first effort  $\mu_{AlGaN} = \mu_n$ ),  $w_j$  is the depletion region under gate,  $w_j = \sqrt{\frac{2\varepsilon_{AlGaN}}{qN_d} \left(V_{bi} - V_{th} - V_g\right)}$ ,  $\varepsilon_{AlGaN}$  is AlGaN dielectric permittivity,  $\varepsilon_{Al_xGa_{1-x}N} = \varepsilon_{GaN} - \left(\varepsilon_{GaN} - \varepsilon_{AlN}\right)x$ ,  $\varepsilon_{GaN}$  and  $\varepsilon_{AlN}$  are dielectric permittivity of GaN and AlN, respectively, x – the Al mole fraction in  $Al_xGa_{1-x}N$ .

The capacitance model includes both intrinsic and extrinsic capacitances. The extrinsic parasitic capacitance of the source and drain metal coupling to the gate metal in air (see Fig.1) is  $C_{\text{ext g}}$ . It is present in both transistor states. Parasitic extrinsic capacitance  $C_{\text{ext sd}}$  couples the source and the drain above the semiconductor, and the intrinsic capacitance  $C_{\text{int sd}}$  couples the same terminals through the semiconductor and substrate; it is present only in the non-conductive off-state, when the 2DEG is suppressed by the gate voltage. These capacitances are estimated using the standard expressions for MESFETs [6]. An extrinsic voltage dependent on-state capacitance between the highy conductive 2DEG and the gate  $C_g$  [7] and intrinsic off-state capacitance between gate and the inner sides of the 2DEG near source and drain  $C_{ig}$  [8] also exists. To compute these capacitaces, equations described in [3-5] were used.

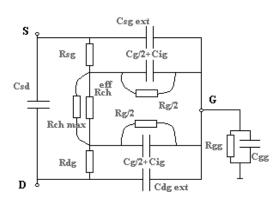

The resulting equivalent circuit is shown in Fig.2. The capacitance  $C_{sd}$  reflects the total extrinsic and intrinsic capacitances between the source and drain. Resistors  $R_S$  and  $R_D$  are assumed small and are omitted in this model. The impedance  $Z_{gg}$  consists of a shunt connected gate resistor  $R_{gg}$  and parasitic capacitance  $C_{gg}$  to ground. Below we consider the situation when the drain is short-circuited to ground.  $R_{gg}$  has several origins and may include the inherent resistance of the gate material, or an intentionally added resistance to aid in keeping the gate floating above ground at high frequencies.

Fig.2 HFET equivalent circuit

## 3. Computed and measured results.

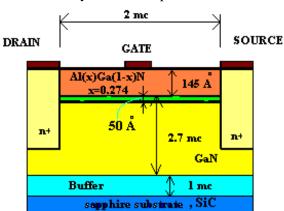

The device layer-structure parameters used for computer and experimental study are shown in Fig.3.

Fig.3 Layer structure of measured HFET

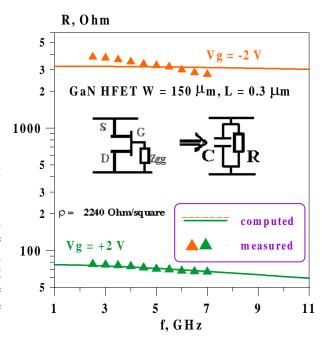

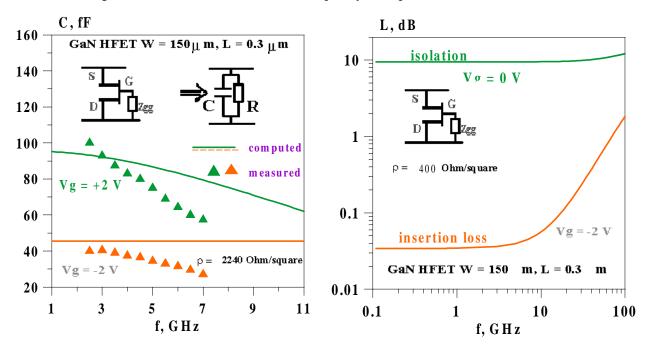

were computed versus frequency. Figures 4 and 5 show theoretical and experimental equivalent shunt resistance and shunt capacitance versus frequency at two gate biases (on and off-state).

Fig.4 shows simulated and measured high frequency properties of the on-state and off-state HFET resistances. **Experiments** showed approximate 10% change with increasing frequency in the resistance at +2.0 volts on the gate over the frequency range 1 to 7 GHz. In the same frequency range the off-state resistance at -2volts has changed about 25%. Fig.5 shows both simulated and experimental capacitance variations with frequency for both switch states. One can see about 40% change in measured on-state capaci-

The room temperature mobility of the 2DEG simulations was 545 cm $^2$ /Vs $^{-1}$ . The gate width used is 150  $\mu$ m, the distance between the source and drain is 2  $\mu$ m, and the gate length is 0.3  $\mu$ m. Using the new modified equivalent circuit model, several general properties of the GaN HFET impedance

Fig.4 HFET resistance vs. frequency

tance and approximately 35% in measured off-state capacitance over the 1.0 to 7.0 GHz frequency range. The model shows better agreement for the on-state than for the off-state capacitance of the transistor. Fig.6 shows the simulated frequency response of shunt the switch's

Fig.5 HFET resistance vs. frequency

Fig.6 Simulated insertion loss and isolation

insertion loss and isolation computed for a sheet resistance of 400  $\Omega$ / . There is little variation in either parameter with frequency below 2GHz while above this frequencya stronger dependence on frequency is observed for both parameters. This is due to the increased reactance from capacitances.

# Conclusion

The focus of this paper is on the investigation into the frequency-dependent microwave and RF control impedance of HFET based on AlGaN/GaN. The investigation resulted in a modification of the current control two-terminal model into three-terminal to include the effects of the gate bias circuit. It was found that the largest variation in switch equivalent circuit parameters (resistance and capacitance) occurred in the on-state GaN HFET. The off-state device showed little variation in either parameter.

## Acknowledgements

This work was supported by the Office of Naval Research (Dr. J. Zolper) under contract number №000149810895. The GaN devices tested were generously supplied by L. Eastman and B. Green of the Department of Electrical and Computer Engineering at Cornell University.

#### References

- [1] U. Mishra, Y-F. Wu, B. Keller, S. Keller, S. Denbaars, "GaN Microwave Electronics", IEEE Trans. on MTT, V.46, pp.756-761, 1998

- [2] M.S. Shur, "GaN Based Transistor for High Power Applications", Solid-State Electronics, V.42, pp.2131-2138, 1998

- [3] N. Drozdovski, and R. Caverly, "GaN Based High Electron Mobility Transistors for Microwave and RF Control Applications", The 1999 Int. Microwave and Optoelectronics Conf., Rio de Janeiro, Brazil, August 9-12, 1999, Proceedings of IMOC'99, pp.490-493

- [4] N. Drozdovski, and R. Caverly, "AlGaN/GaN Material Properties and HFET Shunt Switch RF Performans", The 1999 International Conference on Solid State Devices and Materials, Tokyo, Japan, September21-24, 1999, Extended abstracts of SSDM'99, pp.210-211

- [5] R. Caverly, R., and N. Drozdovski, "GaN Based Transistors for Microwave and RF Control Applications", IEEE Transactions on Microwave Theory and Techniques (in review).

- [6] N.Jain & R.Gutmann "Modeling and design of GaAs MESFET control devices for Broad-band Applications", IEEE Trans. Microwave Theory and Tech., V. MTT-38, No.2, pp. 109-117, February, 1990.

- [7] S.Sze, "Modern Semiconductor Device Physics", Ch. 2, John Wiley and Sons, New York, 1998

- [8] N.Arora,"MOSFET models for VLSI circuit simulation", Springer-Verlag, 1993