# Safety Threshold Predictions of On-Chip Interconnects and Devices Illuminated by High-Power Electromagnetic Pulse (HP-EMPs)

Wen-Yan Yin<sup>1</sup>, J. F. Xu<sup>1</sup>, X. T. Dong<sup>2</sup>, Jun-Fa Mao<sup>1</sup>, Le-Wei Li<sup>2</sup>

<sup>1</sup>Center for Microwave and RF Technologies and School of Electronic Information & Electrical Engineering Shanghai Jiao Tong University, Shanghai 200240, China. Email: <u>wyvin@sjtu.edu.cn</u>

<sup>2</sup> Dept of Electrical and Computer Engineering., National University of Singapore, Kent Ridge, Singapore119260

## Abstract

In the presence of high-power electromagnetic pulse (HP-EMP), electrical and thermal safety thresholds of some onchip interconnects, and passive and active devices are investigated in this paper, directly related to their possible electrical or thermal breakdowns. These safety thresholds include (a) maximum current-carrying density of bonding wires; (b) breakdown field strength of thin film capacitors; (c) peak and average power handling capabilities of conventional microstrip interconnects (MI), finite-ground thin film microstrip (FG-TF-MI) and finite-ground thin film coplanar waveguide (FG-TF-CPW) interconnects: and (d) rise in the maximum channel temperature of GaAs field effect transistors (FET). In order to capture these safety thresholds, efficient nonlinear electromagnetic-thermal coupling finite difference time domain (FDTD) and finite element methods (FEM) are implemented in the numerical computation. These safety thresholds will be useful for further taking electromagnetic protection so as to prevent on-chip device breakdown from attack by an HP-EMP.

## 1. INTRODUCTION

In the environment of high power or high field operating environment, breakdown can be easily taken place when an applied voltage or electric field exceeds the electrical or thermal safety threshold of a dielectric or a device. In a semiconductor device, the breakdown can be physically considered as a random nonlinear transient event in which the electrical, thermal and mechanical interactions are coupled to one another. Only in recent years, researchers have realized very challenging safety problems for on-chip devices, circuits and systems illuminated by a high-power electromagnetic pulse (HP-EMP), because their sizes or geometries are minimized and power supplies are reduced significantly. Even the energy density of an ultra-wideband electromagnetic pulse (UWB-EMP) is much smaller than that of an HP-EMP. such as a high power microwave (HPM) pulse, it is still possible to cause signal jam in a circuit or system, as it is indirectly coupled to an on-chip active device through certain conductive way.

In this paper, we would like to demonstrate some effective ways for predicting electrical and thermal safety thresholds of some on-chip interconnects, passive and active devices in the presence of HP-EMPs, which include bonding wires, TF-CPW-based capacitors, conventional microstrip interconnects, FG-TF-MI and FG-TF-CPW interconnects, RF MEMS switches, and even GaAs field effect transistors. Our motivation is, based on this study, to further explore some effective ways for protecting all the on-chip devices which could be easily broken down.

## 2. OUTLINES OF SAFETY THREHOLDERS OF BONDING WIRES AND TF-CPW-BASED DEVICES

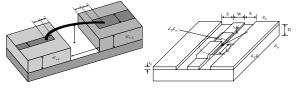

There are many types of interconnects and passive devices used to build various functional blocks of circuits and systems, especially including bonding wires, TF-CPW-based capacitors, spiral inductors, power dividers, and RF switches [1] *etc.* Some views of their three-dimensional structures are shown in Figs. 1(a)-1(c), respectively. The electrical or thermal safety thresholds for different devices can be described by different parameters. For a bonding wire made of aluminum in air, we can use its maximum current carrying density to describe its electrical safety threshold, and it is given by [2]:

(b) TF-CPW-based capacitor

Fig.1. Three-dimensional views of a bonding wire, a TF-CPW-based capacitor, and a RF MEMS switch.

$$J_{\max}^2 \tau \approx 10^8 A^2 \cdot s / cm^4 \tag{1}$$

where  $\tau$  is the duration time of the input current pulse, and *A* denotes the wire cross section. For a TF-CPW-based capacitor, its electrical safety threshold can be characterized by a breakdown field strength  $E_{break}$  or a breakdown voltage  $V_{break}$  of the thin dielectric film. Based on the experimental date given in [3], the value of  $E_{break}$  versus relative permittivity, denoted by  $\mathcal{E}_r$  for most dielectric films, can be described by [3]:

$$E_{break} = 35\varepsilon_r^{-0.64} \left( MV \,/\, cm \right) \,. \tag{2}$$

The electrical safety threshold or the pull-down voltage threshold, denoted by  $V_{\rm max}$ , is a very important indicator in the design of a TF-CPW-based RF MEMS switch, where the air-bridge region can be mechanically broken down. As defined by Katehi *et al.*, the pull-down voltage is determined by [1]

$$V_p = \sqrt{\frac{8k}{27\varepsilon_0 S}g^3} \tag{3}$$

where k denotes the spring constant of the membrane, S stands for the contact area between the membrane and the dielectric, and g represents the gap width between the membrane and the dielectric. Hence, the value of  $V_{\text{max}}$  should be at least larger than  $V_p$ .

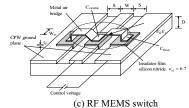

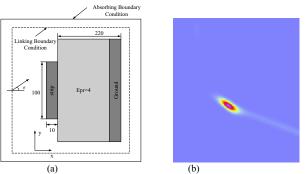

# 3. POWER HANDLING CAPABILITIES (PHC) OF MICROSTRIP AND CPW-BASED INTERCONNECTS

Figs. 2(a)-2(d) show the cross-sectional view of some typical microstrip and CPW interconnects. It should be emphasized that compared to conventional FG-MIs, FG-TF-MIs exhibit different electromagnetic characteristics, because there are significant geometrical differences between them. For example, a FG-TF-MI, as shown in Figs. 2(a), uses a thin dielectric layer of only several or ten microns in thickness deposited on top of a ground plane, and the finite ground plane is deposited onto a carrier substrate, such as GaAs, silicon, or alumina. While the substrate thickness of a conventional FG-MI substrate is usually between 100 to 500 µm, its peak or average PHC will be much larger than that of a FG-TF-MI. Therefore, in the presence of an HP-EMP, FG-TF-MI, FG-TF-CPW or FG-TF-CPW-based devices could be easily broken down, which need to be paid more attention to. Table I summarizes the predicted average PHC of a conventional 50- $\Omega$  MI interconnect on single-layer different substrate materials, respectively. Among all the materials, since the value of BeO thermal conductivity is the largest, the corresponding PHC of a MI interconnect fabricated on a BeO substrate is the highest among all substrate materials, while Teflon-based MI interconnects are only suitable for low-power applications, due to their poor thermal conductivity.

Fig. 2. Cross-sectional views of some microstrip and CPW interconnects.

Table I Comparison of the  $P_{av}$  of a 50- $\Omega$  MI interconnect on singlelayer different substrate materials

| Substrate | $\mathcal{E}_r$ | $\tan \delta$ | <b>D</b> ( µm) | W(µm) | $\Delta T(^{\circ}C/W)$ | $P_{av}(W)$   |

|-----------|-----------------|---------------|----------------|-------|-------------------------|---------------|

| Teflon    | 2.1             | 0.0005        | 1575           | 5013  | 0.4485                  | 0.2787        |

| Quarz     | 3.8             | 0.0001        | 1575           | 3370  | 0.0639                  | 1.956         |

| InP       | 14.0            | 0.0005        | 50             | 30    | 0.0801                  | 1.5605        |

| Sapphire  | 11.7            | 0.0001        | 50             | 37    | 0.09412                 | 1.3281        |

| AIN       | 8.8             | 0.0005        | 25             | 24    | 0.02405                 | 5.200         |

| Duroid    | 2.2             | 0.0009        | 250            | 760   | 0.7771(0.8682)          | 0.1608(0.144) |

| Silicon   | 11.7            | 0.1540        | 100            | 75    | 0.1294(0.126)           | 0.966(0.992)  |

| GaAs      | 12.9            | 0.0010        | 75             | 50    | 0.0788(0.0865)          | 1.586(1.445)  |

| Al2O3     | 9.8             | 0.0002        | 250            | 235   | 0.0298(0.027)           | 4.195(4.630)  |

| BeO       | 6.4             | 0.0003        | 250            | 352   | 0.00246(0.00237)        | 50.8(52.774)  |

| NOSC67    | 4.1(10GHz)      | 0.0050        | 115            | 227   | 0.534                   | 0.2342        |

| China 66  | 7.7             | 0.0003        | 115            | 135   | 0.5205                  | 0.2402        |

| NGK 73    | 7.0             | 0.001         | 115            | 147   | 0.4035                  | 0.3098        |

| IBM 68    | 5.0             |               | 115            | 195   | 0.2331                  | 0.5363        |

| 951-AX    | 7.8             | 0.0005        | 115            | 133   | 0.4462                  | 0.2801        |

| A6M       | 5.9             | 0.0002        | 115            | 170   | 0.4746                  | 0.2634        |

# 4. ELECTROMAGNETIC-THERMAL COUPLING NUMERICAL METHODS AND DISSCUSSIONS

As we have pointed out above, since a breakdown taken place in either dielectrics or semiconductors is a multiple interaction process among electromagnetic, thermal and even mechanical fields. Therefore, temperature issue must be treated appropriately if we want to capture the electrical or thermal safety threshold of a dielectric or an on-chip device numerically. Now we will focus on two methods proposed below.

# (A) Nonlinear FDTD

To obtain the breakdown field strength ( $E_{break}$ ) of a dielectric, we can use nonlinear FDTD combined with high-field conduction model of the dielectric, in which the electrical conductivity of a dielectric are functions of the electric field strength applied and operating temperature. For example, for the dielectric of polyethylene [4], its electrical conductivity can be described by

$$\sigma = \frac{\exp[a + b/T + k \mid E \mid]}{\mid E \mid}$$

(4)

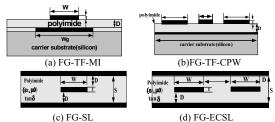

where a, b, and k are three coefficients depending on the dielectric type, |E| is the electric field strength applied, and T is the temperature of dielectric. When an HP-EMP is obliquely incident on this substrate, as shown in Fig. 3(a), the updated equation for electric field component  $E_x$  in the 2D TE case can be written as:

$$E_{x,}^{n+1}\Big|_{i+1/2,j} = \frac{2\varepsilon\Big|_{i+1/2,j} - \sigma_{}^{n+1/2}\Big|_{i+1/2,j}\Delta t}{2\varepsilon\Big|_{i+1/2,j} + \sigma_{}^{n+1/2}\Big|_{i+1/2,j}\Delta t} E_{x}^{n}\Big|_{i+1/2,j} + \frac{2\Delta t}{2\varepsilon\Big|_{i+1/2,j} + \sigma_{}^{n+1/2}\Big|_{i+1/2,j}\Delta t} \times \left(\frac{H_{z}^{n+1/2}\Big|_{i+1/2,j+1/2} - H_{z}^{n+1/2}\Big|_{i+1/2,j-1/2}}{\Delta y}\right)$$

(5)

A similar equation for electric field component  $E_y$  can be also obtained. For each FDTD time step, inner iterations are needed to handle the nonlinear relationship between  $\sigma$  and E, as described by (4). The suffix p represents the pth iteration. In the simulation,  $\sigma$  is defined at half-time steps, and initialized as  $\sigma_{<0>}^{n+1/2} = \sigma^n$ . It is updated based on the electric field of both the pre-step and the current step. Two schemes are available to calculate the conductivity, as shown below:

$$\sigma_{< p+1>}^{n+1/2} \approx \frac{1}{2} \left( \frac{\exp\left[ \left( a + b/T + k \mid E \mid_{}^{n+1} \right) \right]}{\mid E \mid_{}^{n+1}} + \frac{\exp\left[ \left( a + b/T + k \mid E \mid^{n} \right) \right]}{\mid E \mid^{n}} \right)$$

(62)

$$\sigma_{< p+1>}^{n+1/2} \approx \frac{\exp\left[\left(a+b/T+k\left(|E|_{}^{n+1}+|E|^{n}\right)/2\right)\right]}{\left(|E|_{}^{n+1}+|E|^{n}\right)/2}.$$

(6b)

It should be noted that the material properties, *i.e.*  $\mathcal{E}$  and  $\sigma$ , as well as the two current densities  $\vec{J}_r$  and  $\vec{J}_d$  are all defined at the centre of the spatial cell. Therefore, the material properties of two neighbouring grids should be averaged when the field components are calculated. Similarly, an average value of the surrounding field components is needed to obtain the current density at the centre point.

In Fig. 3(a), the permittivity of the dielectric layer is  $\mathcal{E}_r = 4$ , and the conductivity is described by Eq. (4). The incident pulse is a Gaussian pulse, given by  $g(t) = Ae^{-(t-t_0)^2/T^2}$ , where  $t_0 = 1 \times 10^{-13}s$  and  $T = 4 \times 10^{-13}s$ . The FDTD grids are defined as  $\Delta x = \Delta y = 1 \mu m$ , and  $\Delta t = dx/(2C)$ . Fig. 3(b) shows the electrical conductivity in the substrate at a particular time step, with an incident angle of  $\theta = 45^{\circ}$ . Physically, the conductive current density  $(J_c = \sigma E)$  generated in the conducting region, due to the applied HP-EMP, is several times of the displacement current  $(J_a = \varepsilon \frac{\partial E}{\partial t})$ , that is

$$\left|J_{c}(E_{break})\right| = n\left|J_{d}\right|.$$

(7)

So, it can be concluded that electrical breakdown takes place in the conductive region. In Fig. 3(b), the captured breakdown field strength is  $E_{break} = 1.6$  kV/mm when we choose n = 5, which agrees with the value reported in [4].

## (B) Nonlinear FEM

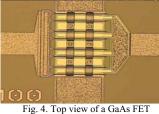

For CPW-built active devices shown in Fig. 4, such as a GaAs effect field transistor (FET), its maximum channel temperature, denoted by  $T_{cmax}$ , is directly related to its thermal

Fig. 3. (a) An HP-EMP is obliquely incident on a microstrip interconnect with  $\theta = 45^{\circ}$ ; and (b) the electrical conductivity generated in the substrate.

safety threshold. As an HP-EMP is suddenly injected into this transistor, the channel temperature will rise rapidly, and as it exceeds the value of  $T_{cmax}$ , the thermal breakdown will be taken place. The HP-EMP can be described by a double exponential pulse as follows:

$$\vec{E}_{in}(t) = E_0(e^{-\beta t} - e^{-\alpha t}) \qquad t \ge 0$$

(8)

where  $\alpha$  and  $\beta$  are two parameters to determine the pulse shape. To accurately characterize the thermal safety threshold of this GaAs FET under the impact of an HP-EMP, we need to sovle a non-linear transient heat conduction equation described by

$$\begin{cases} \rho c_{\rho} \frac{\partial T(x, y, z, t)}{\partial t} + \kappa_{\rho}(T) \nabla^{2} T(x, y, z, t) = g(t) \qquad p = 1, \dots, M \\ T |_{\Gamma_{a}} = T_{0} \qquad (9) \\ \frac{\partial T}{\partial n} |_{\Gamma_{q}} = -h(T - T_{0}) \end{cases}$$

where T(x, y, z, t) represents the temperature distribution in the whole domain of interest;  $\partial T / \partial n$  stands for the normal derivative of the temperature on the boundary;  $\Gamma_a$  is the Dirichlet boundary,  $\Gamma_q$  is the Neumann boundary,  $\kappa_p$  is the thermal conductivity, g(t) is the heat generation rate of the equivalent heat source, *h* is the convective coefficient, and  $T_0$ is the ambient temperature, respectively. In the above GaAs FET, most of the heat is generated at the depletion region produced by the gate. An exact description of the dynamic heating process is very complicated under the illumination of an HP-EMP. Instead, we can assume the heat is generated by a transient source with an equivalent volume source, just embedded under the metal gate. The source length is slightly larger than or equal to the gate length, which is biased towards the drain pad [5].

According to the Ritz differentiation, the functional form of Eq. (9) can be rewritten as:

$$F(T) = \int_{\Omega} \kappa \left\| \nabla \varphi \right\|^2 d\Omega \,. \tag{10}$$

After introducing an FEM interpolation function, the functional form of F(T) in Eq. (10) can be expressed as

$$F^{(e)}(T) \cong \frac{1}{2} \left[ T^{(e)} \right]^T \left[ K^{(e)} \right] \left[ T^{(e)} \right], \tag{11}$$

where  $T^{(e)}$  represents the element temperature vector in the FEM nodes,  $[K^{(e)}]$  is the temperature-dependent element stiffness matrix, whose conformal coefficient is given by

$$K_{ij}^{(e)} = \kappa^{(e)} \int_{\Omega^{(e)}} \nabla N_i \cdot \nabla N_j d\Omega .$$

(12)

The stationary points of the functional  $F^{(e)}(T)$  are obtained by minimizing Eq. (11) with respect to the nodal values of the potential *T*. In this procedure, a linear equation system can be obtained as

$$\left[K^{(e)}\right]\left[T^{(e)}\right] = \left[f^{(e)}\right],\tag{13}$$

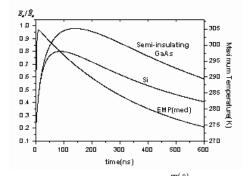

where  $[f^{(e)}]$  is the vector of heat load. To solve Eq.(13) numerically, the iterative scheme of a variant of Newton-Raphson iteration, which makes use of the continuity of the temporal discretion, can be adopted [6]. On the other hand, we should consider the temperature-dependent characteristics of the thermal conductivity of GaAs. Therefore, an additional Newton-Raphson iterative scheme should be adopted [7]. Based on the above formulas, a hybrid FEM code was developed so as to characterize the thermal safety thresholds of some GaAs FETs under the illumination of different HP-EMPs. The thermal boundary conditions on all the boundaries were assumed adiabatic, except that the bottom of the structure was assumed to have a constant temperature of 273K. Thus, the initial temperature was also assumed to be 273K. Fig. 5 shows the variation of the maximum channel temperature  $T_{cmax}$  of a GaAs FET as a function of the pulse duration time. In Fig. 5, the GaAs FET is illuminated by a double exponential pulse (med) with the input power density  $P_{input}$  =1, 2, 3, and 4  $W/\mu m^3$ , respectively. It is obvious that there is time delay between the maximum value of the  $T_{r_{max}}$ and that of the EMP, and all the performance parameters of the GaAs FET will be reduced significantly with increasing the  $T_{c_{max}}$ . Usually, the safety temperature of a GaAs FET should not exceed 100-120  $^{o}C$ ; otherwise, the system will be broken down thermally.

### CONCLUSIONS

In this paper, it has been demonstrated that under the illumination of a high-power electromagnetic pulse, (a) electromagnetic and thermal interactions are strongly coupled to each other in on-chip passive and active devices and circuits; (b) electric filed strength- and temperature-dependent conduction model of the electric conductivity of dielectrics are very important for capturing their breakdown field

strengths numerically; (c) electrical and thermal safety thresholds for most on-chip functional blocks or circuits are still unknown, and there are still some more studies to be further carried out, and (d) in order to prevent on-chip devices and circuits from an intentional electromagnetic attack, the predicted electrical and thermal safety thresholds must be implemented in their design using new structures, new materials combined into advanced fabrication technology.

## ACKNOWLEDGMENT

Wen-Yan Yin and Jun-Fa Mao would like to acknowledge Ministry of Education, China for the Research Grant for *CKSP*, *National Natural Science Foundation of China* for a Research Grant for *Creative Research Groups* via Shanghai Jiao Tong University, *Doctoral Research Foundation* of Ministry of Education, China and the *Pujang Talent Project* of Shanghai, China for their research garnts.

Fig. 5. The maximum channel temperature  $T_{\max}^{(p)}$  versus pulse duration time.

#### REFERENCES

- L. Dussopt and G. M. Rebeiz, "Intermodulation distortion and power handling in RF MEMS switches, varactors, and tunable filters," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-51, no. 4, pp. 1247-1256, 2003.

- [2] K. Banerjee, A. Amerasekera, N. Cheung, and C.Hu, "High-current failure model for VLSI interconnects under short-pulse stress conditions," *IEEE Electron Device Lett.*, vol. 18, no.9, pp. 405-407, 1997.

- [3] J. W. McPherson, J. Kim, A. Shanware, H. Mogul, and J. Rodriguez, "Trends in the ultimate breakdown strength of high dielectric-constant materials," *IEEE Trans. Electron Devices*, vol. 50, no. 8, pp. 1771-1778, 2003.

- [4] S. A. Boggs, "Semi-empirical high-field conduction model for polyethylene and implications thereof," *IEEE Trans. Dielectrics Electr. Insulation*, vol. DEI-2, no. 1, pp. 97-106, 1995.

- [5] W. Y. Yin and X. T. Dong, Investigation on the wave-interactions of ultra-wideband (UWB) electromagnetic pulses and complex PCBs/devices, Internal Research Report No. POD0001968, Temasek Laboratories, National University of Singapore, 2005.

- [6] A. M. Darwish, A. J. Bayba, and H. A. Hung, "Thermal resistance calculation of AlGaN-GaN devices," *IEEE Trans. Microwave Theory Tech.*, vol. 52, no. 11, pp. 2611-2620, 2004.

- [7] J. Park, M. W. Shin, and C. C. Lee, "Thermal modeling and measurement of GaN-Based HFET devices," *IEEE Electron Device Letters*, vol. 24, no. 7, pp. 424-426, July 2003.