### EMC'09/Kyoto

# Equivalent Characteristic Impedance and Propagation Constant for Multi-Layer Via Structures

Siming Pan<sup>#1</sup>, Jun Fan<sup>#2</sup>, and James L. Drewniak<sup>#3</sup>

<sup>#</sup>UMR/MST EMC Laboratory, Missouri University of Science and Technology (formerly University of Missouri-Rolla), Rolla, MO 65409, USA

spmq3@mst.edu

<sup>2</sup> jfan@mst.edu

<sup>3</sup> drewniak@mst.edu

*Abstract*— Via structures in multi-layer printed circuit boards (PCBs) and packages are studied using an equivalent transmission line model. Thus, transmission line theories, such as characteristic impedance and propagation constant, can be used to characterize the performance of via structures in a signal path. The closed-form expressions of R, L, G, C parameters of the equivalent transmission line model are derived based on a physics-based via circuit model with parallel-plane impedances and via-plate capacitances. Effects of geometrical parameters on via equivalent characteristic impedance are studied in the paper as well. The proposed method provides a straightforward approach to design via structures for better signal integrity. Key words: via structures, multi-layer PCBs and packages, equivalent transmission line model, equivalent characteristic impedance, propagation constant, signal integrity.

#### I. INTRODUCTION

Via structures are necessary in multi-layer printed circuit boards (PCBs) and packages to route signals in different layers as well as connect devices to power and ground. However, these structures involve parallel planes, dielectric layers, pads, antipads, and vertical via barrels, and are obviously not ideal transmission lines at high frequencies. Thus the performance of via structures can significantly affect signal and power integrity for high-speed circuits. A physicsbased equivalent circuit model has been proposed to characterize the via behaviors in circuit boards and packages [1]-[4]. However, design and optimization of via structures using the equivalent circuit model is still not straightforward and intuitive. The main objective of this paper is to provide an easy approach to design smooth signal transitions at via connections while maintaining a low insertion loss and minimizing crosstalk, borrowing the concepts such as characteristic impedance and propagation constant from the transmission line theories. Since these concepts/parameters can only be defined for the transverse electromagnetic (TEM) waves, Section II first discusses an equivalent transmission line model to approximate the via structures and then derives the analytical formulas for the per-unit-length R, L, G, C parameters of the equivalent transmission line model. The equivalent characteristic impedance and propagation constant of the via structures can be obtained from the per-unit-length parameters. In Section III, the equivalent transmission line approach is validated by comparing the S-parameter results with the original physics-based equivalent circuit model. Section IV shows a single-ended signal via in a multi-layer

board, with different ground via patterns and antipad sizes, and studies the effects of the geometrical parameters on the equivalent characteristic impedance of the via structure.

### II. EQUIVALENT TRANSMISSION LINE MODEL FOR A SINGLE-ENDED VIA STRUCTURE

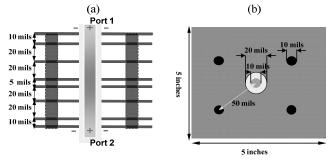

Fig. 1 shows a typical single-ended via structure with multiple neighboring ground vias in a multi-layer PCB. When a current flows on the vertical via barrel, both the ground vias and the multi-layer parallel planes provide its return path. Thus, the transverse magnetic (TM) modes along the vertical via direction can propagate between the parallel planes. Furthermore, the shunt capacitances between the signal via and each plane should be taken into account as well. Therefore, the via structure strictly speaking is not a transmission line, and the per-unit-length parameters cannot be directly extracted from 2D cross-sectional analysis tools.

Fig. 1. (a) Side view; (b) Top view of a single-ended signal via with multiple ground vias

### A. A Physics-based Equivalent Circuit Model

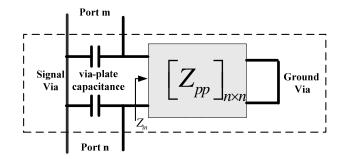

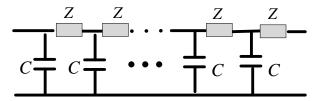

A physics-based circuit model for the via structure has been developed with consideration of the fields between the planes as well as the capacitive coupling between the via and the planes [1]-[4], as shown in Fig. 2. The fields between two parallel planes are modeled as an impedance matrix, namely Zpp herein, which has been extensively studied in the previous publications [5]-[7]. The capacitive coupling between a via and a plane can be modeled as a via-plate capacitance whose analytical expression is provided in [3].

### B. An Equivalent Transmission Line Approach

Although the via structure rigorously speaking is not a transmission line, it can be represented using equivalent

### EMC'09/Kyoto

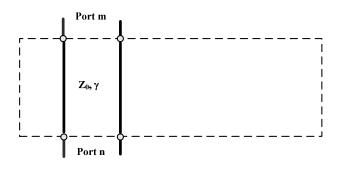

transmission lines. For example, the portion of the via structure between Ports m and n in Fig. 2 can be described as an equivalent transmission line, resulting in an equivalent mathematical model shown in Fig. 3. This mathematical model provides the same network parameters at the ports as the original physics-based model. This further derivation from the physics-based model to the mathematical one provides an opportunity to use the well-known transmission-line concepts such as characteristic impedance and propagation constant for via structure design and optimization.

Fig. 2 A physics-based equivalent circuit model for a single-ended signal via between one parallel plane pair

Fig. 3 An equivalent transmission line model derived from the physics-based model shown in Fig. 2

To derive the parameters of the equivalent transmission line from the physics-based model shown in Fig. 2, the input impedance  $Z_{in}$  looking into the parallel planes at the singleended signal via port *j* with shorting vias at all other via ports can be easily obtained as

$$Z_{in} = \frac{1}{Y_{pp}(j,j)},$$

where  $Y_{pp}$  is the admittance matrix of the parallel plane pair.

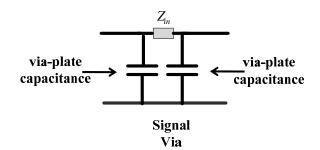

The real part of  $Z_{in}$  represents the losses between the parallel planes, including both the dielectric and skin-effect losses. By employing  $Z_{in}$ , the equivalent circuit model for the single-ended signal via structure can be simplified as shown in Fig. 4.

Generally, the value of  $Z_{in}$  is much smaller than the value of the admittance of the via-plate capacitance when the via length is electrically small. Thus, the lumped circuit in Fig. 4 can be further converted into the distributed circuit in Fig. 5 at the frequencies of interest. The distributed circuit in Fig. 5 is

actually the equivalent transmission line model for the singleended signal via structure, with

$$R = \operatorname{Re}(Z_{in}/l)$$

$$L = \operatorname{Im}(Z_{in}/l)$$

$$C = 2 \cdot C_{v-p}/l$$

$$G = 0$$

where *l* is the length of the via between the parallel-plane pair, and  $C_{v-p}$  is the via-plate capacitance.

The equivalent characteristic impedance  $Z_0$  and propagation constant  $\gamma$  can then be obtained as

1

$$Z_{0} = \sqrt{\frac{Z_{in}}{2 \cdot j\omega C_{v-p}}}$$

$$\gamma = \sqrt{Z_{in} \cdot 2j\omega C_{v-p}} / 2j\omega C_{v-p}}$$

where  $\omega$  is the radian frequency.

Fig. 4 Simplified circuit model from Fig. 2 for a single-ended signal via structure between one parallel plane pair

Fig. 5 Distributed circuit model representing an equivalent transmission line for a single-ended signal via structure between one parallel plane pair

It should be noted that the lumped circuit in Fig. 4 and the distributed circuit in Fig. 5 are equivalent only when the via length is electrically small. In reality, vias behave as a "slow-mode" structure as the equivalent phase velocity of wave propagation is slower than the speed of light in that medium [8]. The "slow-mode" property of vias decreases the frequency range over which the lumped circuit model of Fig. 4 can be converted to a transmission line model.

For multi-layer via structures, the equivalent transmission lines for the portion between each plane pair as discussed earlier can be connected together. Then, via structures can be designed or optimized by matching all the equivalent characteristic impedances and minimizing the loss factors. However, it is usually difficult to match the characteristic impedances layer by layer. Furthermore, as long as via is electrically short, it is unnecessary to consider impedance match at every layer interface. Thus, a multi-layer via structure can be considered as one single transmission line when the via length is electrically small, with

$$R = \operatorname{Re}(\sum Z_{in}/l)$$

$$L = \operatorname{Im}(\sum Z_{in}/l)$$

$$C = \sum C_{\nu-p}/l$$

$$G = 0$$

where  $\sum Z_{in}$  is the sum of the input impedances at the signal via port in every layer, and  $\sum C_{v-p}$  is the sum of all the corresponding via-plate capacitances.

### III. VALIDATION OF THE EQUIVALENT TRANSMISSION LINE APPROACH FOR SINGLE-ENDED SIGNAL VIA STRUCTURES

The following analyses use the cavity model with segmentation technique to calculate the parallel plane impedance [5].

The multi-layer via structure shown in Fig.1 is used as a validation example. The single-ended signal via is located at the center of the board. The thickness of all the copper planes is 0.7 mil. The other geometry details can be found in Fig. 1. All dielectric layers have a dielectric constant of 4.0 and a loss tangent of 0.02.

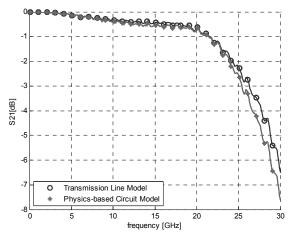

The S parameters between Ports 1 and 2 shown in Fig. 1 are calculated using the original physics-based circuit model as well as the equivalent transmission line model. The results are compared in Fig. 6. At the frequencies below 10 GHz, the results from the two methods agree well, while there are some discrepancies at the frequencies above 10 GHz. The reason is that when frequency is higher than 10 GHz, the via length is comparable to the wave length due to the "slow-mode" property of vias.

## IV. DESIGN IMPLICATIONS FOR THE SINGLE-ENDED SIGNAL VIA STRUCTURE

### A. Design Objective

Smooth transitions between traces and vias, in terms of small insertion loss, small return loss, and linear phase, are desirable for high-speed signal transmissions in multi-layer PCBs and packages. Using the concepts provided by the equivalent transmission line model for the via structures, the equivalent characteristic impedance of via should match with the characteristic impedance of traces. Besides, the frequency-dependent loss of the equivalent transmission line model should be small, which demands the imaginary part of the equivalent propagation constant, to be close to zero. The characteristic impedances of traces are normally 50 Ohms for most of the practical systems, so the single-ended via structure needs to be designed with an equivalent characteristic impedance of 50+j0 Ohms.

B. Geometry Impact on Equivalent Characteristic Impedance

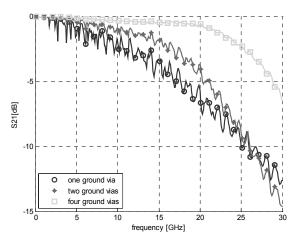

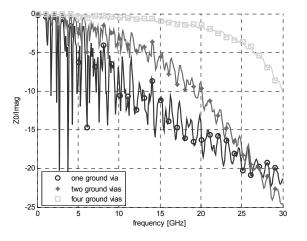

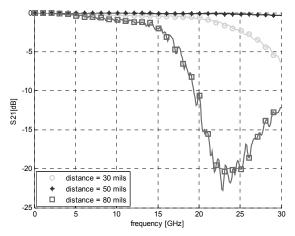

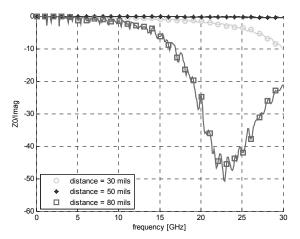

Due to the limitations in manufacturing processes and other design considerations, some geometrical parameters cannot be easily changed, such as board size, dielectric thickness, loss tangent, and drill size, although they can also influence the value of the equivalent characteristic impedance of vias. On the other side, some factors such as the number of ground vias, ground via locations, and antipad radius may be relatively easier to be adjusted in a design to match the equivalent characteristic impedance of vias with trace impedance. Fig. 7 shows  $|S_{21}|$  and the imaginary part of the equivalent characteristic impedance of the via structure in Fig. 1 for different numbers of ground vias symmetrically distributed around the signal via. When the number of the ground vias increases, the imaginary part of the equivalent characteristic impedance decreases, which means dielectric and skin-effect losses become smaller when more ground vias are added. Thus, a better signal path is achieved as the insertion loss becomes closer to zero. This is also true for a shorter distance between the signal via and the ground vias from the results shown in Fig. 8. Therefore, as a rule of thumb, as many ground vias as possible should be used and their distances from signal vias should be minimized.

Fig. 6 (a) Magnitudes of  $S_{11}$  for the single-ended signal via structure shown in Fig. 1

Fig. 6 (b) Magnitudes of  $S_{21}$  for the single-ended signal via structure shown in Fig. 1

Fig. 7 (a)  $|S_{21}|$  of the single-ended via structure shown in Fig. 1 for different numbers of ground vias

Fig. 7 (b) The imaginary part of the equivalent  $Z_0$  of the single-ended via structure shown in Fig. 1 for different numbers of ground vias

Next, the real part of the equivalent characteristic impedance needs to be designed to match with trace impedance. From the earlier discussions, the real part of the equivalent characteristic impedance decreases when the viaplate capacitance increases. The relationship between antipad size and via-plate capacitance is derived in [3]. In other words, the via characteristic impedance can be designed to be close to trace impedance by adjusting the size of antipads.

### V. CONCLUSION

The equivalent transmission line approach proposed in this paper can be used to design and optimize via structures for optimal signal transmissions. The transmission line concepts such as characteristic impedance and propagation constant can provide straightforward and intuitive design parameters. In addition, effects of some geometrical parameters on the performance of a single-ended signal via structure were discussed.

#### REFERENCES

C. Schuster, Y. Kwark, G.Selli, and P. Muthana, "Developing a 'Physical' Model for Vias," DesignCon 2006, Santa Clara, CA USA, Feb.6-9, 2006.

- [2] G. Selli, C. Schuster, and Y. Kwark, M. B. Ritter, and J.L Drewniak, "Developing a Physical Via Model for Vias – Part II: Coupled and Ground Return Vias," DesignCon 2007, Santa Clara, CA USA, Jan.29-Feb 1, 2007.

- [3] Y. Zhang, J. Fan, G. Selli, M. Cocchini, D. P. Francesco, "Analytical Evaluation of Via-Plate Capacitance for Multilayer Printed Circuit Boards and Packages," IEEE Trans. Microwave Theory Tech., vol. 56, no. 9, pp. 2118-2128, Sep. 2008.

- [4] G. Selli, C. Schuster, Y. Kwark, J. Drewniak, "Modelto-Hardware Correlation of Physics Based Via Models With the Parallel Plate Impedance Included", *IEEE* Symposium on Electromagnetic Compatibility, Portland, OR, USA, August 2006.

- [5] G.T. Lei, R. W. Techentin, P. R. Hayes, D. J. Schwab, B. K. Gilbert, "Wave Model Solution to the Ground/Power Plane Noise Problem", IEEE Transactions on Instrumentation and Measurement, Vol. 44, No. 2, April 1995.

- [6] R. Chadha, K.C. Gupta, "Segmentation Method Using Impedance Matrices for Analysis of Planar Microwave Circuits", IEEE Transactions on Microwave Techniques, Vol. MTT-29, No.1, January 1981.

- [7] M. Xu, Y. Ji, T. H. Hubing, T. P. Van Doren, and J. L. Drewniak, "Development of a closed-form expression for the input impedance of power-ground plane structure," in Proc. IEEE Int. Symp. Electromagn. Compat. Washington, DC, Aug. 2000, pp. 77-82.

[8] X. Gu, A. Ruehli, M. Ritter, "Impedance Design for Multi-layered

- [8] X. Gu, A. Ruehli, M. Ritter, "Impedance Design for Multi-layered Vias", Electrical Performance of Electronic Packaging, 2008 IEEE-EPEP, pp. 317-320.

Fig. 8 (a)  $|S_{21}|$  of the single-ended via structure shown in Fig. 1 for different distances between signal and ground vias

Fig. 8 (b) The imaginary part of  $Z_0$  of the single-ended via structure shown in Fig. 1 for different distances between signal and ground via