# Analysis of 2-Layers Metallic Substrate Module for an Automotive BLDC Motor Driver

Sang-Kook Kim<sup>#,\*1</sup>, Chang-Gyun Kim<sup>&,\*2</sup>, Tae-Heon Lee<sup>\*3</sup>, Jin-Yong Jeon<sup>#4</sup>, Seog-Moon Choi<sup>+5</sup>, and Jae-Kyung Wee<sup>\*6</sup>

<sup>#</sup> R&D Center, Hyundai Autonet Co. Ltd at South Korea <sup>1</sup>13stone@chol.com <sup>4</sup>jeonjy@hyundaiautonet.com <sup>&</sup> ROOTiN Technology at South Korea

<sup>2</sup>rudra@rootin.com

<sup>&</sup>R&D Center, Samsung Electro-Mechanics Co., Ltd <sup>5</sup>sms.choi@samsung.com

<sup>\*</sup>School of Electronics, Soongsil University at South Korea

<sup>3</sup>aaa@ssu.ac.kr

<sup>6</sup>wjk@ssu.ac.kr, correspond

*Abstract*—This paper reports design method and characteristic analysis of a 2-layers metallic substrate module for a turbo charger BLDC motor driver. A module design methodology is suggested to protect system performance degradations of a 2-layers PCB system compared with a 4-layers system. A design flexibility of 2-layers PCB is limited because power-ground planes and signal traces have to share the same planes. Also, the thermal problem is more critical than 4 layers module. For the avoidance of these problems, the 2layers metallic substrate module was designed with the design concept considered about thermal spreading pattern, PI, EMC and current return paths. The results of the 2-layers metallic module show the good performance on thermal spread characteristic and EMI characteristic to meet the given system compliance.

### I. INTRODUCTION

Nowadays, the electronic system in the automotive is growing significantly up to 23 percent of the total manufacturing cost [1-2]. For cost-down, reducing the number of passive components and low cost modules are becoming hot issues owing to a competitive price in recent market. However, the needs to more complex, high speed and powerdissipated electrical systems are going to make a large barrier to low cost approaches of one or two layers module and package and skip of inevitable passive components, and so on.

In this paper, instead of a conventionally used 4-Layers PCB for BLDC motor driver of a turbo charger in automotive, a 2-Layers module is designed and tested for manufacture qualification. Generally, to improve the signal integrity or EMI, it requires at least a 4-Layers PCB design. Because, 2-Layers PCB has limitation on the power and the ground plane as signal traces have to share with the planes [3]. 2-Layers PCB system makes an unstable return path and ground bounce by unsteady distribution of power/ground plane compared with 4-Layers PCB system [4][5]. Also, induced noise and EMI by inductance of signal line and power network can be seriously considered because of its high power consumption.

Fig. 1 shows the turbo charger system working to engine which directly mounts the BLDC drive module. The turbo charger system must require stable and high level performance. The first of them, thermal problem should be considered for preventing the heat generation and spreading the local heat.

In this paper, the 2-layer based design to solve problems in heat, signal integrity, power integrity and EMI of a BLDC motor drive module are proposed and verified with several tests on operation function, EMI, and thermal spread. Due to guaranteeing high power consumption operations under high temperature atmosphere in a car engine, module substrate is selected with metallic ( $Al_2O_3$ ) material which is supported from Samsung Electromechanics Co. Ltd.

Fig. 1 BLDC motor driver module on a turbo charger in the automotive.

### II. THEORY

Fig. 2 is a flow chart of the proposed PCB design for an efficient 2-Layers PCB design. In a 2-Layers PCB system, problems are appeared in thermal problem as well as power integrity, signal integrity and EMI. The devices layout, PCB layout and topology must be considered for preventing the heat generation and spreading the generated heat from the

# EMC'09/Kyoto

design early stage since, in case of PCB system on engine room, thermal problem is very important. So, the substrate material should be also selected with proper consideration. In addition, the isolation patterns of power/ground plane and irregular power-to-ground shapes cause the unwanted simultaneous switching noise (SSN) [5][6].

Fig. 2 PCB design methodology

Also, they make uncontrollable resonance peaks on selfand trans-impedance characteristics in PCB [7]. In view of signal integrity, line crosstalk, impedance mismatching, reflection and termination effect as important factors that cause problems to the signals are dependant on the power network as well as signal lines [8]. Since the proper modelling should be adapted for reduction of calculation time and resource, the operation conditions such as differential modes, common modes and frequency wavelengths of signals must be properly considered. After pre-design stage of the given system, the layout is performed. But, PCB layout must also be re-designed after that PCB design ruler checks the module layout for protection of the problems caused by power integrity, signal integrity and EMI. The design rule check library should be prepared for each system specification. Especially, the automotive system requires a strict rule to guarantee the safety. Therefore, the entire design rule is set with distinguishing a design method of "the PCB Routing Ruler and PI/SI/EMI Design Guideline for the automotive". This rule can be used in the process to the reference layout as a verifying rule and in a device manufacture stage after modification for the post-layout. After a stage of the post design and sensitivity check for manufacturability, if there is no problem on the final design check, the design processing step is over. The high value impedance can change a low current noise to high voltage noise. So, noise problem is decreased by lower impedance of a transmission line. The unwanted impedance peaks within the frequency bandwidth generated by a power/ground resonance. are The power/ground resonances should be suppressed for the relatively lower impedance than target impedance within the

operation bandwidth that affect to noise. This problem can be solved by using the stitching vias method. Additionally, the stitching vias has the effect of EMI reduction [9].

### III. DESIGN PRACTICE

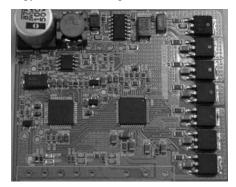

In this section, the three key items are discussed for 2layers design without the system performance degradation. The designed 2-layers PCB board is 67.71mm x 57.08mm. Fig. 3 shows the fabricated BLDC motor driver designed by the methodology as shown in Fig. 2.

Fig. 3 Fabricated BLDC Motor driver

### A. Thermal Problem

Table I shows the geometrically compared data between FR4 and metallic Substrate(AMS) for the BLDC drive module which is designed for reducing the thermal problem. For this, a part of power MOSFETs is located near at the edge side to be isolated for spreading heat and reducing the effect of switching noises on other chips. Especially, thermal problem is very important because this system is mounted on the car engine directly. The high power consumption system makes the temperature increasing by parasitic resistance worse because of addition heats of an engine system. It degrades rapidly down the system performance and makes the system fail. According to equation referred in [10], the temperature variation is related to the values of resistance and current. If the current value is fixed, thermal problem can be controlled by regulating the resistance value. Therefore, in the line design, the signal line width is proposed at 53 mils owing to considering heat generation by line resistivity.

$\begin{tabular}{l} TABLE \ I \\ THE COMPARISON BEWTEEN FR4 AND AMS (METALLIC SUBSTRATE) \\ \end{tabular}$

|                       |                               | FR 4       | AMS                                     |          |  |

|-----------------------|-------------------------------|------------|-----------------------------------------|----------|--|

|                       | Cu                            | 385W/m-K   | Cu                                      | 385W/m-K |  |

|                       | FR4                           | ~0.3W/m-K  | Al <sub>2</sub> 0 <sub>3</sub>          | 30W/m-K  |  |

| Structure             |                               |            | Aluminum                                | 200W/m-K |  |

|                       |                               |            | Al <sub>2</sub> 03                      | 30W/m-K  |  |

|                       | Cu                            | 385W/m-K   | Cu                                      | 385W/m-K |  |

| Thermal<br>Resistance |                               | >50K/W     |                                         | <5K/W    |  |

| Sub. Size             | ze 10 x 10 mm²(Thick.: 0.5mm) |            | 10 x 10 mm <sup>2</sup> (Thick.: 0.5mm) |          |  |

| Cost                  |                               | 0.15\$/per | 0.15\$/per                              |          |  |

The topologies of a detailed line are choose as length of 5 inch and copper thickness of 2Oz under maximum dc current 2A and a guarantee of 120 c.

### B. Routing Problem

# EMC'09/Kyoto

Noises would be generated on a line generate radiated emissions and conducted emissions which have the trade-off with design-area efficiency. In this PCB design, line width is decided due to physical pitch of selected pad and lead in IC package and line width should be selected for low impedance that crosstalk. Generally, a copper thickness in 2-layers PCB is applied thicker than a copper thickness in multi-layers PCB. Table II shows calculated the proper values between a current and a line width for tolerable temperature increase.

TABLE II A CURRENT AND LINE WIDTH

|   | Temperature | Current | Copper        | Length | Width |

|---|-------------|---------|---------------|--------|-------|

|   | [°C]        | [A]     | Thickness[Oz] | [inch] | [mil] |

| ſ | 120         | 5       | 2             | 5      | 13.72 |

### C. Electrical Design

The via stitching method can be applied to attenuate noises that is caused by ground bounce, simultaneous switching noise, power/ground resonance in power integrity. The viastitching method can be a solution to control power crosstalk on board. Also, it can reduce the coupling phenomenon of the microstrip lines in signal integrity. The via holes are disposed uniformly to keep off the spread of power/ground resonance.

For lower susceptibility, conducted emissions should be suppressed under target level. One of methods to solve is to maintain the constant pitch of signal lines in switching device. The line space is constant in the signal lines. There are holes on the copper plane, which is expected to reduce the EMI radiated between the copper planes as a shielding wall.

The key issue in 2-layers PCB is the radiation by ground loop current. It is designed to guarantee width of ground plane as large as possible, and to place few signal line at the bottom side for stable ground return path. Fig. 4 shows the part of bottom side used as ground plane in layout. Ground plane is used with hatched copper.

Fig. 4 The bottom side of layout.

### IV. SIMULATIONS

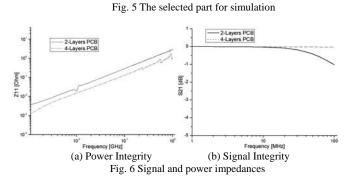

The 2-layers PCB board designed by suggested PCB design methodology is simulated for signal integrity and power integrity. To compare their simulated results with target design from them of 4-layer PCB, the usability of the proposed 2-layer design method is proved through comparison with simulations. The selected signal line is a part of output line for using PWM method of BLDC motor controller. Fig. 5 shows the signal line and power domain selected for the simulation. The path on the output of power MOSFET is 21Q3-3

selected for signal integrity and the self impedance of power domain is selected at input power point. Measured point for power integrity

l por

Fig. 6 (a) is input impedance plots of board's input port for power supply of system. According to the simulation result, the input impedance of 2-layers PCB is higher than the 4layers PCB on the whole frequency bandwidth. The impedance difference is about  $9m\Omega$  at the 8MHz. Fig. 6(b) shows the simulated S21 results. Although, overall frequency range, the S21 value of 2-layers PCB is lower than 4-layers PCB's S21 value, the BLDC motor drive module is operated at the maximum 8MHz frequency bandwidth. At the 8MHz frequency bandwidth, there is no difference between simulated results from the 2-layers PCB and target specs from 4-layers PCB.

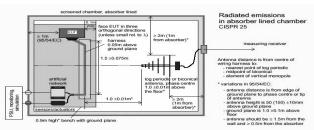

Fig. 7 EMI (Electromagnetic Interference) test environment

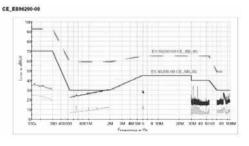

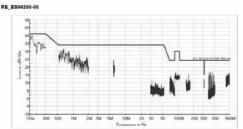

Generally, a motor driver module is designed with 4-layers PCB due to EMI and EMC characteristics, or frequently designed by using more multiple-layers PCB. Fig. 7 shows the international standard CISPR25 test environment for EMI CE(Conducted Emission) and RE (Radiated Emission). Fig. 8(a) and 8(b) show the evaluated results of CE and RE according to test manual of Fig. 7. Its test results satisfy the compliance of EMI CE and RE, which shows the possibility of the proposed standard design method to 2-layers PCB

# EMC'09/Kyoto

design. In addition, this design approach can be brought to more efficient fail analysis as well as reduced PCB layers and more improved performance.

(a) Conducted Emission

(b) Radiated Emission

Fig. 8 Test results of EMI

(a) Test feature for IR thermography

(b) Conventional Package (FR4)

(c) SEMCO AMS (Al substrate)

Fig. 9 Prepared modules of thermal test and the photographs of thermal test results. Metallic substrate module is supported from Samsung Electromechanics Co. Ltd.

Tests have been carried out to compare the thermal performance between AMS® (Anodized Metal Substrate; Samsung ElectroMechanics LTD.'s trade mark) and conventional FR4 PCB. Under the same input thermal power 12W, the temperature differences between these two kinds of substrates after SMT process have been measured using IR camera. As shown in the graph, the temperature differences between chip (heat source) and substrate are 29.2°C for AMS and 98.4°C for conventional FR4 PCB, respectively, i.e. the thermal resistances are 2.43K/W for AMS and 8.2K/W for FR4 PCB. It can be seen from the test results that substrate's thermal performance is a critical factor to improve the device's thermal performance and therefore, the thermal

21Q3-3

performance of SMT processable substrate is very important to keep the device's functional performance.

TABLE III

COMPARISON OF FR4 SUBSTRATE AND METALLIC SUBSTRATE

| Test Result & Input Value | Thermal Characteristic |         |         | Input Power |  |

|---------------------------|------------------------|---------|---------|-------------|--|

| Test Result & Input value | Chip                   | Board   | ΔΤ      | input rower |  |

| Conventional PKG (FR-4)   | 137.3 °C               | 28.9 °C | 98.4 °C | 12W         |  |

| AMS PKG (Al)              | 62.6 °C                | 33.4 °C | 29.2 °C | 12W         |  |

#### VI. CONCLUSIONS

The 2-layers metallic-base PCB for the BLDC motor driver is designed for solving a thermal problem, which is directly mounted on the engine of an automobile. Also, the design methodology is considered in manufacturing cost, as well as signal integrity, power integrity, EMI. Under these considered items, the system must satisfy robust performance reliability because it operates in hard environment such as physical vibration, high power consumption and high level temperature environment. The proposed design validity is evaluated through comparison with tests. The test results show that our design approach using the 2-layer metallic PCB can be another candidate for automotive module requiring low cost and high reliability.

#### ACKNOWLEDGMENT

This work was supported by Next-generation growth engine project of the Korea Ministry of Commerce, Industry and Energy.

#### REFERENCES

- Ziebart, W., "Future Automotive Electronic Systems and Their Impact on Solid-State-Circuits", Solid-State Circuits Conference, 1992. Digest of Technical Papers. 39th ISSCC, 1992 IEEE International, pp. 20-22, 19-21 Feb. 1992

- [2] Leen, G., Heffernan, D., "Expanding Automotive Electronic Systems", Computer Volume 35, Issue 1, pp. 88-93, Jan. 2002.

- [3] Goh Ban Hok, "A Study of High Speed Implementation for System on Chip on 2 Layers Printed Circuit Board", Integrated Circuits, 2007. ISIC '07. International Symposium, pp. 150-153, 26-28 Sept. 2007.

- [4] H. J. Liaw et al, "Signal integrity issues at split ground and power planes", Proc. 46Ih IEEE Electronic Comp. Technol. Conf., pp. 152-755, 1996.

- [5] C.T.Wu, and et al "Composite effects of reflections and ground bounce for signal line through a split power plane", IEEE Trans. Adv. Packaging, Vol. 25, pp. 297-301, May 2002.

- [6] Smith, L., "Simultaneous Switch Noise and Power Plane Bounce for CMOS Technology", Electrical Performance of Electronic Packaging, 1999, pp. 163-166, 25-27 Oct. 1999.

- [7] Zhi Liang Wang, et al, "Application of Segmentation Method to Analysis of Power/Ground Plane Resonance in Multilayer PCBs", Electromagnetic Compatibility, 2002 3rd International Symposium, pp. 775-778, 21-24 May 2002.

- [8] Goyal, R., "Managing Signal Integrity[PCB Design]", Spectrum, IEEE Volume 31, Issue 3, pp. 54-58, March 1994.

- [9] Xiaoning Ye, et al., "EMI mitigation with multilayer power-bus stacks and via stitching of reference planes", Electromagnetic Compatibility, IEEE Transactions on Volume 43, Issue 4, pp. 538 - 548, Nov. 2001.

- [10] C. Kim, "Module Design Using 2-Layers PCB for an Automotive BLDC Motor Driver", in Proc. IEEE EDAPS, (Coex, Korea) pp. 109-112, DEC. 2008.