# Multi-Port Test for Quasi-Static Lumped Element Stand-Alone Model

Umberto Paoletti #1, Takashi Hisakado #2, Osami Wada #3

<sup>#</sup>Department of Electrical Engineering, Graduate School of Engineering, Kyoto University, Kyoto Daigaku Katsura, Nishkyo-ku, Kyoto 615-8510, Japan <sup>1</sup>paoletti@circuit.kuee.kyoto-u.ac.jp

Abstract— The stand-alone package modeling scheme is aimed at estimating the high frequency electromagnetic coupling between different types of packages and external structures, such as printed circuit board (PCB) traces and power/ground planes, or other stacked packages, by limiting at the same time the disclosure of internal details of the package itself. The package is at first modeled in stand-alone conditions, that is without any PCB, by using all the detailed information. In the second stage the interaction with a particular PCB is taken into account with a simplified model, which can be open to the public and also reduces the complexity of the calculation. The quasi-static lumped element stand-alone model is one of the possible implementation of this modeling scheme. In the present paper this model is used to calculate the interaction of a scaled quad flat package (QFP) model with two PCBs having different configurations. The results are compared with the measurement results obtained with a 4port network analyzer.

# I. INTRODUCTION

Due to the high density of interconnects it is very common to use imperfect ground planes below ball grid array (BGA) packages. For application where board costs are a major issue, imperfect ground planes below or near QFPs are also used. The PCB configuration below or very close to the package affects the electrical characteristics of the package at high frequencies, and should be considered during signal or power integrity analysis. Sometimes traces run on the board below or close to the package, and the coupling between traces and package can become important.

For these reasons, package and PCB should be analyzed together, based on detailed information of the overall system. However, very often in practice the PCB designer does not have detailed information about the internal geometry of IC and package, particularly for cost-performance ICs. Furthermore, the simulations can become too complex in this way.

An alternative model which is often used in practice is a very simplified package model, which is obtained by measurement or simulations assuming a PCB of fixed thickness and a perfect ground plane. As already mentioned, this solution is not satisfying at high frequencies.

From here comes the need of a package model that can be adapted to different PCB thicknesses and layouts, and that at the same time limits the open details of the structure, in order to respect proprietary information, and to reduce the complexity of modeling the overall system. The proposed solution is to use a new type of package model, that we called stand-alone package model [1]. In section II the stand-alone package modeling technique is introduced, together with one possible example of standalone model, that is the quasi-static lumped element standalone model. In section III the latter is used to predict the effect of two different ground patterns on the four-port impedance of a scaled QFP model with a simplified IC power-ground structure.

# II. STAND-ALONE PACKAGE MODEL

#### A. General description

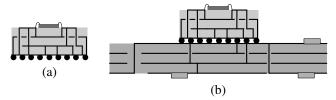

In general terms the idea consists of a model of a package without PCB in free space conditions, as schematically shown in Fig. 1(a) for a BGA package. The model is later modified and adapted to a particular PCB by considering the mutual coupling, as shown in Fig. 1(b). The key point is that in the calculation of the interaction with the PCB only a simplified model is needed.

Fig. 1. Package in stand-alone conditions (a) and with PCB (b).

The idea is not limited to the interaction with the PCB, but it can be applied also to the interaction between IC and package by starting from an IC model in stand-alone conditions. In the second stage, when the model is applied to a particular package, the original model is modified and a new stand-alone IC-package model is prepared, which can be later used with any PCB. In this way the complexity and information given to the successive design stage is limited, by keeping at the same time the flexibility of application of the model.

The stand-alone model consists of two parts: the internal and the external equivalent models. The internal equivalent model represents the electrical characteristics of the package without PCB in free space conditions. Additionally, for those parts of the package that are relevant for the external coupling, the external equivalent model describes or somehow represents the near electromagnetic field (or electric and magnetic field separately) in stand-alone conditions, when they are excited by some unitary sources.

In order to prepare the stand-alone model, a detailed description of the package is necessary. However, when the model is used to calculate the coupling with a PCB, all this information is not required. In fact, the application of the model consists of two steps. One step is the calculation by means of the external model of the interaction between the package and the rest, for example some traces on the PCB. The second step is the modification of the internal model due to the external environment, for example the PCB ground plane. The fundamental assumption of the model is that the effect of the environment on the external equivalent model is negligible.

The concept of stand-alone modeling is not strictly limited to one particular technique, and it can assume different expressions depending also on the frequency range and on some design selections. In the following, one example of realization of this modeling scheme is presented, for the frequency range where the quasi-static approximation can be applied.

# B. Quasi-static lumped-element model

The quasi-static lumped element stand-alone model can be strictly applied only to packages much smaller than the wavelength. The internal model consists of partial element equivalent circuits, such as partial self and mutual inductances, capacitances and resistances. The external model consists of equivalent structures, which can be used to calculate the electric and magnetic interaction with the environment, separately.

For example, for the magnetic coupling equivalent segments which approximately follow the conductor paths can be used. For the electric coupling, equivalent patches in air can be used. The dimension of the patches can be calculated as the product of an equivalent area and an equivalent dielectric constant. In this way, detailed information of the package does not need to be disclosed.

The parameters of the model, such as dimension, position and equivalent dielectric constant, should be determined with a preliminary analysis. However, even by selecting the parameters with some simple rules of thumb, a reasonable accuracy can be obtained, as we will show in the example in the following section.

Each equivalent element of the external model must be associated with some parts of the internal model. The application of the model consists of the separate calculation of the electric and magnetic interaction between the equivalent segments and patches of the external model and the PCB. Thanks to the simplification of the geometry, the calculation burden is significantly reduced.

### III. EXAMPLE OF APPLICATION

Even though for high frequency applications mainly BGA packages are used, a 4:1 scaled model of a QFP has been selected here, in order to be able to prepare the package and a simplified IC structure in the laboratory with moderate costs and preparation time. The real target of the present example is not modeling the QFP itself, but it is modeling the electromagnetic interaction between PCB and package in terms of the stand-alone modeling scheme. The fact that in a BGA package the distance between package and PCB is usually shorter, is not really an issue, because it can be handled anyway by decreasing the dimensions and increasing the number of partial elements in the model if necessary. The presence of balls is also not a limitation, because they can be probably treated with some particular equivalent model. Furthermore, the information regarding the geometry of the balls is open.

### A. Description of the DUT

The DUT is a 4:1 scaled model of a QFP with 48 leads, and it is schematically shown in Fig. 2. The package model consists of a PCB of 0.8 mm thickness, some pins representing the vertical parts of the package leads, and some short traces on the top layer of a second PCB, representing the ends of the leads at the soldering position. In the figure the package model is enclosed in the red dashed line, a complete lead is enclosed in the blue dotted line, and a vertical pin is enclosed in the black dashed and dotted line.

Fig. 2. Cross section of the DUT (mm).

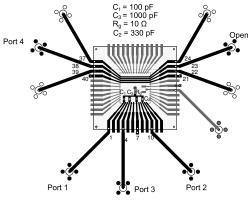

Furthermore, in order to separate the problem of package modeling from that of IC modeling, and to simplify the measuring setup, a very simple structure has been etched on the top PCB, representing some simple IC interconnections, as shown in Fig 3. One part of the simplified IC structure is connected to leads 1, 4, 10 and 7, and consists of surface mount capacitors (100 pF, 1000 pF and 330 pF) and a resistor (10  $\Omega$ ), respectively, representing three IC power/ground impedances. The second structure for evaluation consists of 4 parallel traces between the leads 21-24 and 37-40. The remaining parts of package and IC models are in gray color in the figure, and are not relevant to the present experiment.

Fig. 3. Target of the measurement.

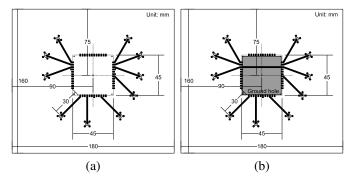

Two slightly different configurations have been used for the bottom PCB, as shown in Fig. 4. In both PCBs lead 7

is connected to the bottom ground plane, and 30 mm traces (1.5 mm width) are connected at the leads 1, 4, 10, 18, 22, 23, 24, 37, 38 and 39. Five traces are attached to SMA connectors, namely those connected at the leads 1, 4, 10, 23 and 38. Only a few of the upper and lower parts of the 48 leads on the top and bottom PCBs, are vertically connected through pins, namely leads 1, 4, 7, 10, 18, 21, 23, 24, 37, 38 and 40.

PCB (a) of Fig. 4(a) has a full ground plane, three additional pin connections between the top and bottom parts of the package at the leads 19, 22 and 39, and three additional via connections to the bottom PCB ground plane at the leads 19, 21 and 40, which are also indicated with red in Fig. 3. PCB (b) of Fig. 4(b) has a large rectangular hole in the ground plane below the package (green in the figure), and a 1.5 mm wide trace connecting the leads 22 and 39 below the package on the top layer of the bottom PCB.

Fig. 4. PCB patterns without (a) and with (b) hole in the ground plane.

### B. Quasi-static lumped-element model for QFP

The package model consists of an RLC network with mutual inductances. Within the quasi-static approximation, it is possible to approximately calculate the partial equivalent circuit elements with FASTCAP [2] and FASTHENRY [3]. This is only an approximation, because the partial capacitances and inductances are calculated separately, without considering the reciprocal effect of the current and charge distributions.

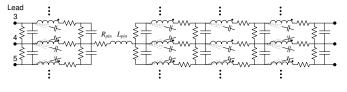

Each lead is divided into five PI-type stages, including a series connection of one resistance and one inductance representing the vertical pin, which is not coupled with all the remaining inductances in the model, as shown in Fig. 5. All the remaining inductances represent partial inductances, and have been calculated in standalone conditions.

Fig. 5. Internal model of 3 consecutive leads.

The series resistances represent the conductor losses and have been calculated together with the inductances at 1 GHz. The partial capacitances have been calculated in standalone conditions with FASTCAP. The shunt resistances represent the dielectric losses, and the corresponding conductance G has been calculated at 500 MHz from the capacitance C and a constant loss tangent (tan  $\delta$ ).

In the case of the full ground plane of PCB (a), one single reference ground can be used. For the PCB (b), where the cut in the ground plane is present, one reference ground for each lead has been used. Each ground node is connected to the adjacent ones by means of partial inductances and resistances, forming a loop all around the aperture in the ground plane, as shown in Fig. 6. These parameters as well have been calculated with FASTHENRY, together with all the mutual inductances with the external equivalent model and with the PCB trace.

Fig. 6. Equivalent circuit of package with cut ground plane.

The shunt capacitance of package and IC models to PCB ground and trace can be calculated with the external equivalent model, by calculating the capacitances to the PCB ground and trace of the equivalent rectangular patches in air. The calculation is very much simplified by the absence of the package dielectric substrate, and by the fact that the patches are considered separately, one for each calculation.

The effect of the PCB on the internal model was limited to the inductances in the present example.

### C. Measurement and simulation results

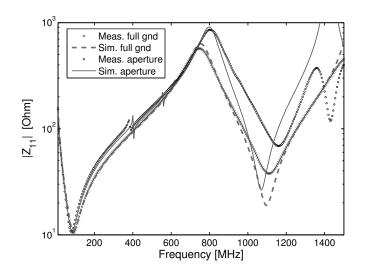

Four-port measurements have been conducted for both PCBs of Fig. 4 with a vector network analyzer connected at the ports according to Fig. 3. The 30 mm traces and the SMA connectors have been de-embedded. From the resulting scattering matrix, the 4-port impedance matrix has been calculated. In the measurement results shown in Fig. 7, it can be observed that the large hole in the ground plane increases the impedance at port one and introduces some resonances.

The increase in the impedance below 600 MHz is related to the inductive coupling with the loop formed by the ground plane around the aperture. The increase in the impedance above 800 MHz is due to the reduction of the capacitance to the ground plane, which is caused by the aperture.

The resonance at around 400 MHz is due to the inductive coupling between the main loop formed by the leads 1 and 7, and the loop formed by the combination of the aperture, the trace across the aperture, and the microstrips connected at the leads 22 and 39. In the simulations a second resonance appears

Fig. 7. Driving point impedance with and without cut on the ground plane.

around 600 MHz. This second resonance is due the inductive coupling between the main loop and the loop formed by the combination of the aperture, the connection through the IC structure between the leads 24 and 37, and the microstrips connected at these leads. By looking at the scattering parameters, which are not shown for the sake of compactness, it can be observed that this resonance is present in the measurement data as well, but it is much more dumped. This means that in the simulation the losses have been underestimated, for example in the pin resistance including solder, which directly affects this resonance. The ground resistance has a similar effect on the Q-factor of both resonances at the same time, due to the relatively large current flowing all around the aperture at the resonance frequency.

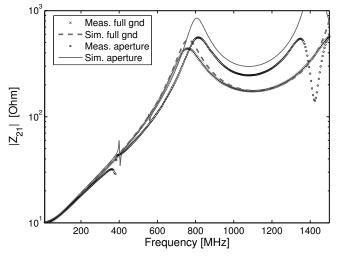

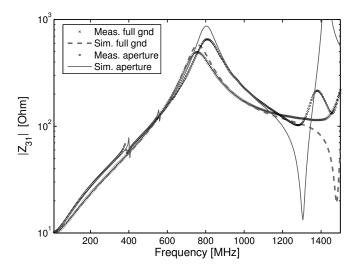

In the Figs. 8 and 9 the transfer impedances between port one, and ports two and three are shown. Generally a good agreement for the board with full ground can be observed up to almost 1.5 GHz. Some exceptions are the resonances and antiresonances, which can be probably corrected by improving the dielectric and conducting losses. The effect of the radiated power has not been estimated yet.

For the board with aperture there is generally a good agreement up to around 900 MHz. Above this frequency the effect of the capacitance is not always correctly estimated. However, this is not necessarily due to the the stand-alone model itself, but it can be due to the particular circuit layout used for modeling the PCB.

### **IV. CONCLUSIONS**

The proposed quasi-static lumped-element stand-alone model made it possible to estimate the effect of the high frequency electric and magnetic coupling between package and PCB based on a restricted amount of information regarding the internal layout. The model showed an interesting agreement with multi-port measurements, even if it has been obtained on the base of simple "first-order" rules. A refinement of the model can probably further improve the results.

Fig. 8. Transfer impedance with and without cut on the ground plane.

Fig. 9. Transfer impedance with and without cut on the ground plane.

The proposed quasi-static lumped-element model is only the first example of the more general stand-alone modeling scheme. An extension to other types of stand-alone models is expected to be done in future work.

#### ACKNOWLEDGMENT

The presented work has been carried out within a collaboration project supported by STARC (www.starc.or.jp).

### REFERENCES

- U. Paoletti, T. Hisakado, and O. Wada, "Quasi-Static Lumped Element Stand-Alone Package Model for Quad Flat Package," in *Proc. 2008 Electrical Design of Advanced Packaging and Systems (EDAPS) Symposium*, Seoul, Korea, Dec. 2008, pp. 57–60.

K. Nabors and J. White, "Multipole-accelerated capacitance extraction al-

- [2] K. Nabors and J. White, "Multipole-accelerated capacitance extraction algorithms for 3-D structures with multiple dielectrics," *IEEE Transactions* on Circuits and Systems-1, vol. 39, no. 11, pp. 946–954, Nov. 1992.

- [3] M. Kamon, M. J. Tsuk, and J. White, "A Multipole Accelerated 3-D Inductance Extraction Program," in *Proc. 30th international conference* on Design automation, Dallas, Texas, 1993, pp. 678–683.