# A Charge-Based SiC Power MOSFET Model Considering On-State Resistance

Rui Zhou, Michihiro Shintani, Masayuki Hiromoto, and Takashi Sato

Graduate School of Informatics, Kyoto University Yoshida-hon-machi, Sakyo, Kyoto 606-8501, Japan Email: paper@easter.kuee.kyoto-u.ac.jp

**Abstract**—Transistor models have been playing a key role in designing efficient power converters. As the operating frequency of the converters becomes higher, transistor models need to represent physical device behavior accurately and compactly. In this paper, we propose a charge-based transistor model that considers gradual transition between linear and saturation regions, and parasitic resistances of vertical diffused SiC power MOSFET. Transient simulation using the proposed model, as well as I-V and C-V characteristics, matched well with the experimental results using a commercial device.

# 1. Introduction

Silicon Carbide (SiC) is considered as one of the most promising materials for realizing power converters that operate with high power density and at a high frequency. Accurate circuit simulation is crucial to optimally design power converters. The simulation accuracy greatly depends on the accuracy of the SiC power device model.

Fitting-based equations have been widely used as the SiC power MOSFET model [1]. These models are recognized to efficiently simulate the electrical behavior of the SiC power MOSFET. However, in such models, prediction of the physical phenomena, such as process variation and reliability of SiC, is difficult because the mathematical model does not contain physically meaningful parameters that actually varies in real devices. Also, the characteristics outside the fitting region may not be sufficiently accurate.

Recently, inversion charge-based transistor models have been successfully applied for designing silicon-based integrated circuits. The charge-based models can accurately reproduce behavior of silicon devices computationally efficiently [2, 3]. However, charge-based model has not yet been applied to the models of SiC vertically double diffused MOSFETs (VDMOSFETs). Model equations have to be modified to represent I-V characteristics. In particular, parasitic resistances associated with the vertical current flow in the vertical double diffused structure have to be accurately modeled.

In this paper, we propose an accurate SiC power MOS-FET model based on the channel charge. The proposed model takes into account the bias dependence of the parasitic resistances of the VDMOSFET. The capacitance characteristics are represented by the analytic expressions proposed in [4]. The I-V, C-V, and transient characteristics of the proposed model have been validated through experiments using a commercial SiC device.

## 2. Charge-Based Model

The charge-based model is a compact device model that is widely used for simulating silicon-based MOSFETs. On the basis of single equation, the charge-based model can accurately and consistently predict the circuit performance [2, 3]. No concatenation of separate equations is required to represent full operational range of the device. This is one of the advantages over the conventional models, such as [5]. Another advantage of the charge-based model is its efficiency. The drain current is accurately obtained through an analytic expression that represents inversion charge density at the source and drain electrodes.

We adopt EKV model [2] as the basis of our proposed model. The drain current  $I_{DS}$  is represented as [6]:

$$I_{\rm DS} = \beta \int_{V_{\rm S}}^{V_{\rm D}} \frac{-Q_{\rm i}}{C_{\rm OX}} \mathrm{d}V. \tag{1}$$

Here,  $V_D$  and  $V_S$  are drain and source voltages, respectively.  $\beta = \mu C_{OX} \frac{W}{L}$  is the transmission coefficient, being *L* the channel length, *W* the channel width,  $\mu$  the carrier mobility, and  $C_{OX}$  the oxide capacitance per unit area. Although Eq. (1) is an accurate expression of the physical current flow, it involves numerical integration of the inversion charge  $Q_i$ . Its computational cost is in general too high for use as the compact device model. In the EKV model, the inversion charges at the drain and source ends of the channels are approximated to facilitate analytic calculation. With this approximation, the drain current is obtained with a small calculation time.

The EKV model considers the inversion charge  $Q_i$  in both strong and weak inversion regions. When the body effect is sufficiently small, by solving the Poisson's equation at the surface of the channel, the inversion charge is written as

$$Q_{i}(strong inv.) \simeq -nC_{OX}(V_{P} - V_{ch}),$$

$$Q_{i}(weak inv.) \simeq -K_{w}C_{OX}U_{T}\exp\left(\frac{V_{P} - V_{ch}}{U_{T}}\right). \quad (2)$$

Here,  $V_{\rm P}$  is the pinch-off voltage,  $V_{\rm ch}$  is the electric potential in the channel, and  $U_{\rm T}$  is the thermal voltage. In addition,  $n \equiv 1 + \gamma/(2\sqrt{\Psi_0 + V_{\rm ch}})$  and  $K_{\rm w} \equiv (n - 1)^{-1}$

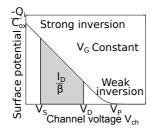

Figure 1: Drain current according to Eq. (4).

1) exp { $(\Psi_0 - 2\Phi_F)/(U_T)$ }.  $\gamma$  is the substrate bias factor,  $\Psi_0$  is the channel surface potential at  $V_{ch} = 0$ ,  $\Phi_F$  is the Fermi potential, and  $V_{T0}$  is the threshold voltage at the zero bias. The pinch-off voltage  $V_P$  is defined as follows:

$$V_{\rm P} = V_{\rm G} - V_{\rm T0} - \gamma \left[ \sqrt{V_{\rm G} - V_{\rm T0} + \left(\frac{\gamma}{2} + \sqrt{\Psi_0}\right)^2} - \left(\frac{\gamma}{2} + \sqrt{\Psi_0}\right) \right].$$

(3)

Figure 1 illustrates the surface potential as a function of  $V_{ch}$  at a constant gate voltage  $V_{G}$ .  $V_{ch}$  varies from zero to  $V_{P}$ , and the surface potential also changes according to  $V_{ch}$ .

The current that flows from the source to the drain (forward current  $I_F$ ) is obtained by integrating  $Q_i/C_{OX}$  from  $V_S$ to infinity. Similarly, by integrating from  $V_D$  to infinity, the current from the drain to the source (reverse current  $I_R$ ) is obtained. Because the drain current  $I_{DS}$  is the difference between  $I_F$  and  $I_R$ ,  $I_{DS}$  can be expressed as follows:

$$I_{\rm DS} = I_{\rm F} - I_{\rm R} = \underbrace{\beta \int_{V_{\rm S}}^{\infty} \frac{-Q_{\rm i}}{C_{\rm OX}} dV}_{\text{Forward current } I_{\rm F}} - \underbrace{\beta \int_{V_{\rm D}}^{\infty} \frac{-Q_{\rm i}}{C_{\rm OX}} dV}_{\text{Reverse current } I_{\rm R}}.$$

(4)

In order to calculate  $I_{\text{DS}}$  by Eq. (4),  $I_{\text{F}}$ ,  $I_{\text{R}}$ , and the transition between  $I_{\text{F}}$  and  $I_{\text{R}}$  need to be modeled.  $I_{\text{F}}$  and  $I_{\text{R}}$  can be derived from Eq. (2). In the EKV model, the smoothing function is introduced to fit the transition.

## 3. Charge-Based SIC Power MOSFET Model

## **3.1.** Overview of the Proposed Device Model

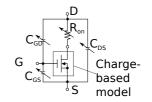

In this section, the proposed charge-based SiC power MOSFET model is explained. Figure 2 shows the structure of the proposed model. The drain current  $I_{DS}$  is expressed based on the charge-base model described in Sec. 2.

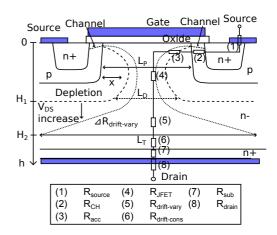

The proposed model assumes the VDMOSFET structure shown in Fig. 3. The VDMOSFET has the parasitic resistances on its current path, total of which is on-resistance  $R_{on}$ . The value of each resistance is voltage dependent. Hence, all voltage dependencies of the on-resistances has to be correctly modeled in order to accurately simulate the current characteristic of the SiC power MOSFET.

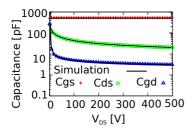

The parasitic capacitances,  $C_{GS}$ ,  $C_{DS}$ , and  $C_{GD}$ , are also modeled considering the dependencies to the drain-source voltage  $V_{DS}$  and the gate-source voltage  $V_{GS}$ . In the proposed model, the capacitance model proposed in [4] is used.

Figure 2: Structure of the proposed model.

Figure 3: Cross section of the VDMOSFET with parasitic resistances.

#### 3.2. Drain Current Model

In order to apply the charge-based model to SiC VD-MOSFETs, the following changes have been made.

- Mobility degradation due to interface traps at the SiC/SiO<sub>2</sub> [7] has been considered.

- Bias-dependent on-resistances of VDMOSFET [8, 9] have been considered.

According to the measurement results of the drain current of SiC power MOSFETs, the transition between linear and saturation regions occurs more gradually than silicon transistors. The smooth transition is considered to be caused by high density of interface states in the inversion channel [7]. When body effect coefficient is sufficiently small, Eq. (3) can be rewritten as  $V_P = V_{GS} - V_{T0}$ . However, this equation is insufficient to express the gradual transition. Through the observations on the measured I-V characteristics, we found that the gradual transition can be modeled by modifying the pinch off voltage as:

$$V_{\rm P} = N_{\rm GS} (V_{\rm GS} - V_{\rm T0})^{\alpha} + N_{\rm DS} [(V_{\rm GS} - V_{\rm T0})^2 V_{\rm DS}]^{\zeta}, \quad (5)$$

where  $N_{\rm GS}$ ,  $N_{\rm DS}$ ,  $\alpha$ , and  $\zeta$  are fitting parameters.

Figure 3 shows the cross section of the VDMOSFET. The on-resistance  $R_{ON}$  for this vertical structure is defined by considering the following resistances: source terminal resistance  $R_{source}$ , drain terminal resistance  $R_{drain}$ , substrate resistance  $R_{sub}$ , accumulation resistance  $R_{acc}$ , channel resistance  $R_{CH}$ , JFET resistance  $R_{JFET}$ , constant drift region resistance  $R_{drift-cons}$ , and variable drift region resistance

$R_{\text{drift-var}}$ . Here,  $R_{\text{source}}$ ,  $R_{\text{drain}}$ ,  $R_{\text{drift-cons}}$ , and  $R_{\text{sub}}$  are constant resistances determined by the geometry of the VD-MOSFET.

$R_{\rm acc}$  is the variable resistance. According to [8], due to the charge density of accumulation layer,  $R_{\rm acc}$  becomes  $V_{\rm GS}$ dependent

$$R_{\rm acc} = \frac{1}{\frac{W}{L} \mu C_{\rm ox} (V_{\rm GS} - V_{\rm T0})}.$$

(6)

$R_{\text{JFET}}$  is also the variable resistance formed at the JFET region.  $R_{\text{JFET}}$  limits the drain current path by the width of the depletion layer that depends on  $V_{\text{DS}}$ .  $R_{\text{JFET}}$  can be written as

$$R_{\rm JFET} = \frac{\rho l}{L_{\rm D} W}.$$

(7)

$L_{\rm D}$  is the distance between depletion layers, and it is defined as  $L_{\rm D} = L_{\rm P} - 2x$ . Here,  $L_{\rm P}$  is the distance between adjacent p regions. W is the channel width, l is the vertical depth of the JFET region, and  $\rho$  is the receptivity of the JFET region.  $L_{\rm D}W$  expresses the cross-sectional area of the JFET region. The width of the depletion layer x is given as

$$x = \sqrt{\frac{2\varepsilon_{\rm sic}}{q}} \frac{N_{\rm A} + N_{\rm D}}{N_{\rm A}N_{\rm D}} (V_{\rm bi} + V_{\rm DS}), \tag{8}$$

where  $V_{\text{bi}}$  is the built-in voltage,  $\varepsilon_{\text{SiC}}$  is the permittivity of SiC, q is the elementary charge, and  $N_{\text{D}}$  and  $N_{\text{A}}$  are the densities of donors and acceptors, respectively. By applying  $V_{\text{DS}}$ ,  $L_{\text{D}}$  changes. Combining the above equations,  $R_{\text{JFET}}$  becomes:

$$R_{\rm JFET} = \frac{\rho h}{L_{\rm D} W} = \frac{\rho h}{\left(L_{\rm P} - \sqrt{\frac{2\varepsilon_{\rm sic}}{q} \frac{N_{\rm A} + N_{\rm D}}{N_{\rm A} N_{\rm D}}} (V_{\rm bi} + V_{\rm DS})\right) W}.$$

(9)

In the model of  $R_{\text{drift-vary}}$ ,  $H_1$  and  $H_2$  are defined as the depths from the substrate-surface of the device.

As shown in Fig. 3, by supposing *s* as the cross-sectional area of the  $R_{\text{drift-vary}}$  between  $H_1$  and  $H_2$ ,  $R_{\text{drift-vary}}$  can be expressed as follows:

$$R_{\rm drift-vary} = \int_{H_1}^{H_2} \frac{\rho}{s} dh, s = W \left( L_{\rm D} + \frac{L_{\rm T} - 2L_{\rm D}}{H_2} l \right).$$

(10)

where  $L_{\rm T}$  is the distance between adjacent source terminals. Therefore, Eq. (10) can be rewritten as follows:

$$R_{\text{drift-vary}} = \int_{H_1}^{H_2} \frac{\rho}{W(L_{\text{D}} + \frac{L_{\text{T}} - 2L_{\text{D}}}{H_2}l)} dh$$

=  $C_1 V_{\text{DS}} + \log(V_{\text{DS}}) + C_2 V_{\text{DS}} + C_3.$  (11)

Here,  $C_1$ ,  $C_2$ , and  $C_3$  are the coefficients represented by using device dimensions and physical parameters.

The on-resistance  $R_{ON}$  of the VDMOSFET is considered as the series connection of all the above parasitic resistances. Thus, by arranging the sum of the parasitic resistances as  $N_1$ – $N_5$ ,  $R_{on}$  is expressed as follows:

$$R_{\rm on} = \frac{N_1}{(V_{\rm GS} - V_{\rm T0})} + N_2 V_{\rm DS}^{\zeta} + \frac{N_3}{N_4 - \sqrt{V_{\rm DS} + V_{\rm bi}}} + N_5. \ (12)$$

Table 1: Model parameters of current characteristic

| Domonator             | Evaluation                                                                             | Value                 |

|-----------------------|----------------------------------------------------------------------------------------|-----------------------|

| Parameter             | Explanation                                                                            | value                 |

| Ψ <sub>0</sub> [V]    | Surface potential when $V_{\rm ch} = 0$                                                | 6.22                  |

| V <sub>T0</sub> [V]   | Threshold voltage at zero bias                                                         | 5.31                  |

| N <sub>GS</sub>       | Coefficient of $V_{\rm P}$ on $V_{\rm GS}$                                             | $1.81 \times 10^{-1}$ |

| α                     | Multiplier of $V_{\rm P}$ on $V_{\rm GS}$                                              | 1.60                  |

| N <sub>DS</sub>       | Coefficient of $V_{\rm P}$ on $V_{\rm DS}$                                             | $7.52 \times 10^{-4}$ |

| ζ                     | Multiplier of $V_{\rm P}$ on $V_{\rm GS}$                                              | 1.13                  |

| $\mu C_{\rm ox}$      | Transconductance                                                                       | $3.61 \times 10^{-3}$ |

| $N_1$                 | $\frac{W}{L\mu C_{OX}}$                                                                | 8.79×10 <sup>-3</sup> |

| N <sub>2</sub>        | Coefficient of $R_{\text{drift-vary}}$                                                 | $1.50 \times 10^{-2}$ |

| <i>N</i> <sub>3</sub> | $ ho l \sqrt{rac{q N_{ m A} N_{ m D}}{2 arepsilon_{ m sic} (N_{ m A} + N_{ m D}) W}}$ | 1.09                  |

| $N_4$                 | $C \sqrt{rac{q N_{ m A} N_{ m D}}{2 arepsilon_{ m sic} (N_{ m A} + N_{ m D})}}$       | 41.27                 |

| $N_5[\Omega]$         | Fixed resistance                                                                       | $2.09 \times 10^{-1}$ |

|                       |                                                                                        |                       |

Table 2: Model parameters of capacitance characteristic

| Parameter           | Explanation                  | Value                  |

|---------------------|------------------------------|------------------------|

| $V_{\rm bi}$ [V]    | Built-in voltage             | 2.01                   |

| $V_{\rm td}$ [V]    | Threshold drain voltage      | $5.52 \times 10^{-1}$  |

| $C_{\rm GS}(0)$ [F] | $C_{\rm GS}$ at zero bias    | 5.38×10 <sup>-10</sup> |

| $C_{\rm DS}(0)$ [F] | $C_{\rm DS}$ at zero bias    | 3.07×10 <sup>-10</sup> |

| $C_{\rm GD}(0)$ [F] | $C_{\rm GD}$ at zero bias    | 2.23×10 <sup>-10</sup> |

| Coxd [F/Vs]         | Gate-drain oxide capacitance | $4.11 \times 10^{-3}$  |

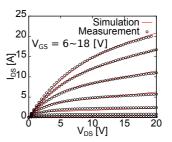

Figure 4:  $I_{DS}$ - $V_{DS}$  characteristics.

#### 4. Experimental Results

The proposed device model is validated using a commercial SiC power MOSFET (1200V, 10A, [10]). I-V and C-V characteristics of the SiC power MOSFET are measured by a commercial curve tracer [11]. The proposed device model is implemented by Verilog-A. I-V, C-V, and transient characteristics are calculated by a commercial circuit simulator [12]. Model parameters are determined by a simulated annealing method [13]. The Model parameters used in the proposed model for I-V and C-V characteristics are summarized in Table 1 and 2, respectively.

#### 4.1. I-V and C-V Characteristics

The measured and simulated current and capacitance characteristics are compared in Figs. 4 and 5. In Fig. 4,  $V_{GS}$  is varied from 6 V to 18 V with a 2 V step. In Fig. 5, capacitance values are measured from  $V_{DS} = 0$  V to  $V_{DS} =$

Figure 5: C-V<sub>DS</sub> characteristics.

Figure 6: Circuit schematic of double pulse tester.

Figure 7: Measured (solid) and simulated (dashed) waveforms.

500 V. The fitting results of the proposed model agree very well with the measurement. Through the adjustment of  $V_P$  and parasitic resistances in the preceding chapter, the mean square error of current characteristic is reduced to 0.24 A.

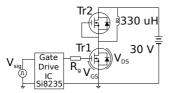

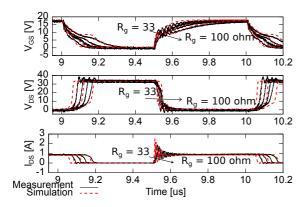

# 4.2. Transient Characteristic

The transient characteristic is evaluated using a double pulse tester circuit shown in Fig. 6. The switching frequency is 1 MHz and the pulse duty factor is 50%. The gate series resistance  $R_g$  is varied as 33, 47, 68, and 100  $\Omega$ . Figure 7 shows both simulated (solid black) and measured (dashed red) waveforms at turn-on and turn-off periods. The proposed model can accurately simulate the switching waveforms of the SiC power MOSFET for all  $R_g$  values.

But simulation wave pattern of  $V_{\text{DS}}$ ,  $I_{\text{DS}}$  is earlier than measurement. It is thought that this does not consider the parasitic ingredient in the actual survey circuit by the circuit simulation of this experiment.

### 5. Conclusion

In this paper, we proposed a charge-based model for SiC power devices considering the structure of the VDMOS-FET. The proposed model also takes into account the gradual transition between linear and saturation regions due to interface traps. Experimental results using a commercial SiC power MOSFET show that the proposed simulation model accurately reproduces I-V, C-V, and transient characteristics.

# Acknowledgments

This work has been partially supported by Kyoto Super Cluster Program (JST) and Cross-ministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics" (NEDO).

## References

- [1] Keysight Technologies, Inc., "IC-CAP device modeling software," Aug. 2014.

- [2] C.C. Enz and E.A. Vittoz, "Charge-based MOS transistor modeling," pp.13–55, John Wiley & Sons, 2006.

- [3] Y.S. Chauhan, S. Venugopalan, et al., "BSIM6: Analog and RF compact model for bulk MOSFET," IEEE Trans. Electron Devices, pp.234–244, 2014.

- [4] N. Phankong, T. Funaki, and T. Hikihara, "Characterization of the gate-voltage dependency of input capacitance in a SiC MOSFET," IEICE Electronics Express, vol.7, no.7, pp.480– 486, 2010.

- [5] University of California, Berkeley, "Bsim4v4.7, MOSFET model," 2011. [Online]. Available: http://www-device. eecs.berkeley.edu/bsim/Files/BSIM4/BSIM470.

- [6] H.C. Pao and C.T. Sah, "Effects of diffusion current on characteristics of metal-oxide (insulator)-semiconductor transistors," Solid-State Electronics, vol.10, pp.927–937, 1966.

- [7] S. Potbhare, N. Goldsman, A. Akturk, M. Gurfinkel, A. Lelis, and J.S. Suehle, "Energy-and time-dependent dynamics of trap occupation in 4H-SiC MOSFETs," IEEE Trans. Electron Devices, vol.55, no.8, pp.2061–2070, 2008.

- [8] B.J. Baliga, Fundamentals of Power Semiconductor Devices, Springer Science & Business Media, 2008.

- [9] H.A. Mantooth, K. Peng, E. Santi, and J.L. Hudgins, "Modeling of wide bandgap power semiconductor devices – part I," IEEE Trans. Electron Devices, vol.62, no.2, pp.423–433, 2015.

- [10] ROHM Semiconductor, "SCT2450KE N-channel SiC power MOSFET datasheet," May 2013.

- [11] Keysight Technologies, Inc., "B1505A power device analyzer/curve tracer," July 2015.

- [12] SIMetrix Technologies Ltd., "SIMetrix SPICE and mixed mode simulation," Oct. 2012.

- [13] S. Kirkpatrick, C.D. Gelatt, and M.P. Vecchi, "Optimization by simulated annealing," Science, vol.220, no.4598, pp.671–680, 1983.