# 分岐機構を強化したSIMD型並列コンピュータの開発 Development of an SIMD parallel computer with enhanced branch mechanisms

# 大部 雄也† Katsuya Ohbe

# 1.まえがき

SIMD型マシンは構造が簡単で高並列度の実現が容易である。しかし従来のものは単純な分岐機構のため多数の分岐命令を含む複雑なプログラムの処理は困難である。そこでMIMD型マシンで通常使用されるSPMD型プログラムをそのまま実行できるような新しい分岐機構をSIMD型マシンに付加する事を考えた。従来のものでは分岐条件を満たさないプロセッサ要素(PE)は無条件にスリープ状態となり、制御プロセッサ(CP)から送られる命令を無視するようになっている。もしもすべてのPEが分岐条件を満たさなければ、その間CPから送られるスレッドは実行されないのでその時間が無駄になる。このような事態をさけることのできる新しい分岐機構を開発した。

# 2.SIMD型マシン

SIMD型並列マシンの構造はMIMD型のものに比べ簡単であるため、高並列度の並列処理実現が容易である.しかし単一命令の並列同時処理という事で、処理能力に限度が生じる.また分岐命令に対する動作が貧弱である為に、多数の分岐命令を含むプログラムを処理する際、多くの無駄なスレッドを排出し多大なタイムロスが生じる事もある[1][2].今図1のプログラムを実行したとする.

A;

IF(条件 1){ B;

IF(条件 2) C;

ELSE D;

} ELSE E;

F;

WHILE(条件 3) G;

H;

図1 分岐命令を含むプログラム

A , B , C , . . . , Hは独立した命令群(スレッド)である.従来のSIMD型ではСPからPEに対し(A)(B)(C)(D)(E)(F)(G)・・・(G)(H)という順にスレッドを送りPEはそれらを実行する.また Program 内に生じる条件分岐に対しては,条件を満たすPEのみが実行を行う.ここで1つ問題が生じる.例えばもしすべてのP

†大阪工業大学大学院情報科学研究科 Graduate School of Information Science, Osaka Institute of Technology ‡大阪工業大学情報科学部 Faculty of Information Science, Osaka Institute of Technology

# 高橋 義造‡ Yoshizo Takahashi

Eが(条件1)を満たしたならば(E)は無駄なスレッドになってしまう.またその逆にすべての PE が(条件1)を満たさなければ,(B)(C)(D)は無駄なスレッドとなってしまう.従来のSIMD型では,このような状況を解決するために,タグやマスクレジスタでPEの状態を記録しそれぞれのPEとCPが通信を行う事で無駄なスレッドの発生を回避している[1].この考え方は簡単なプログラム構造の際には効果的であるが,多大な数のPEが存在する場合や条件分岐が複雑に存在する場合の実現は非現実的である.そこで,どのような場合にも柔軟に対応可能な新しい分岐機構を考えた.

#### 3.新しい分岐機構

#### 3.1 アーキテクチャ

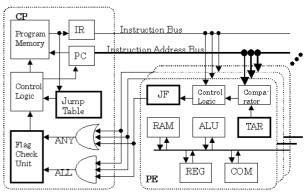

図2は新しい分岐機構を持つCPとPEのアーキテクチャである.

図 2 新しい分岐機構をもつ C P と P E の アーキテクチャ

図 2 において JumpTable (JT), FlagCheckUnit (FCU), JumpFlag (JF), TargetAddressRegister (TAR)が新しく付加したものである. 更に CP が現在 実行している命令のアドレス番地を Instruction Address Bus に送信するので PE が実行アドレスを確認する事が可能になる.

# 3.2 分岐動作

分岐動作には前方分岐と後方分岐が存在する.表 1 はそれぞれの動作について表したものである.表 1 のように前方分岐と後方分岐では動作が異なる.前方分岐の場合には,PE は分岐条件を満たすと TAR に分岐後のアドレスを格納し JF を立ち上げスリープ状態に入る.その後 Instruction Address Bus により CP の実行しているアドレスを確認し TAR の値と一致すれば JF を下げ通常動作に戻る.また CP は前方分岐の際,JF の数を確認し

表1 分岐命令におけるCPとPEの動作

| CP/PE | 分岐先  | 状態             | 動作                           |  |  |  |

|-------|------|----------------|------------------------------|--|--|--|

| CP    | 前方分岐 | ALL=1          | PC=JT(MIN); *1               |  |  |  |

|       |      | ALL=0          | PC++;                        |  |  |  |

|       | 後方分岐 | ANY=1          | PC=operand;                  |  |  |  |

|       |      | ANY=0          | PC++;                        |  |  |  |

| PE    | 前方分岐 | 分岐条件を<br>満たす   | JF=1;<br>TAR=operand; sleep; |  |  |  |

|       |      | 分岐条件を<br>満たさない | JF=0;                        |  |  |  |

|       | 後方分岐 | 分岐条件を<br>満たす   | JF=1;                        |  |  |  |

|       |      | 分岐条件を<br>満たさない | JF=0;<br>TAR=PC+1; sleep;    |  |  |  |

すべてが立ち上がっていれば(ALL=1)前方全体分岐を 行う.その際の分岐先アドレスは JT によって決められ る.これに対し後方分岐の場合には,PE は分岐条件を 満たすと JF を立ち上げるだけでよい . そして CP は1 個でも JF が立ち上がっていれば (ANY=1)後方全体分 岐を行う .また条件を満たさない PE は TAR に現在のア ドレスに'1'を加えた値を格納しスリープ状態となる.ス リープの間の動作は前方分岐の際と同じで CP の実行ア ドレスを確認し、TARの値と一致すれば動作を再開する. つまり,後方分岐の際は前方分岐とは逆に1つでも PE が後方分岐を必要とすれば全体で必ずその位置に分岐 することになる.

このように動作する事で動作全体の無駄を可能な限 り省略し,最適な処理動作を行う分岐機構である.

#### 3.3 Jump Table

条件分岐の際,分岐中に分岐が生じる二重分岐などの 多重分岐の場合がある、その中でも特に前方分岐中の前 方分岐の際には特に注意が必要である. 例えば外側の前 方分岐の際に特定の PE が条件を満たし JF を立ち上げ たとする.次に内側の前方分岐に残りすべての PE が条 件を満たすと、この時点ですべての JF が立ち上がる (ALL = 1).この場合 CP は無条件に2つ目の分岐先に 全体分岐を行なう.しかし1つ目の分岐先が2つ目の分 岐先より前のアドレスであると,矛盾が生じてしまう. そこでこのような状況にならないように,分岐先アドレ スを格納する JT というレジスタを PE の数だけ付加し てある. そして,前方分岐の度に JF を確認し,1個で も JF が立ち上がっていれば(ANY = 1)分岐先アドレ スを JT に記録しておく、また常に最小値にポインタを 指定しておき,全体分岐の際にはその値を使用する(表1 \*1).この JT により多重分岐であっても確実な分岐先ア ドレスが確保される.

### 4. 実行

実際の動作について考えてみる.今,PE2台のSIMD 型マシンで図3のプログラムを,3台で図4プログラム を実行したとする.図3における3.・6.は前方分岐,図 4における4.は後方分岐である.表2は図3のプログラ ムを実行した場合の,表3は図4のプログラムを実行し た場合の結果である.

| 1.      | 1d                     | X   |        |                             |    |

|---------|------------------------|-----|--------|-----------------------------|----|

| 2.      | cmp                    | У   |        |                             |    |

| 3.      | jm                     | els |        |                             |    |

| 4.      | 1d                     | ь   | •      |                             |    |

| 5.      | st                     | а   | 1.     | 1d                          | Х  |

| 6.      | jmp                    | fin | 2. do: | sub                         | У  |

| 7. els  | ld.                    | d   | 3.     | cmp                         | У  |

| 8.      | st                     | С   | 4.     | jp                          | do |

| 9. fin: | equ                    | *   | 5.     | st                          | X  |

|         | カ方分岐を<br>プログラ <i>L</i> |     |        | を<br>カラショク<br>カログラ <i>ロ</i> |    |

PE 2 EXE 0

EXE 0

EXE ALL

EXE 0

EXE

EXE

0

(1)PE1 のみが分岐条 (2)PE1,PE2 共に分岐条

| 件を両に9 |     |     |     | 14を | 満に  |

|-------|-----|-----|-----|-----|-----|

| 命令    | PE1 | PE2 | JF  | 命令  | PE1 |

| 1     | EXE | EXE | 0   | 1   | EXE |

| 2     | EXE | EXE | 0   | 2   | EXE |

| 3     | EXE | EXE | ANY | 3   | EXE |

| 4     | _   | EXE | 0   | 7   | EXE |

| 5     |     | EXE | 0   | 8   | EXE |

| 6     | _   | EXE | ANY | 9   | EXE |

| 7     | EXE |     | 0   |     |     |

| 8     | EXE |     | 0   | _   |     |

| 9     | EXE | EXE | 0   | 表   | ₹2( |

(3)PE1.PE2 共に分岐 条件を満たさない

| PE 1 | PE2                      | JF                              |

|------|--------------------------|---------------------------------|

| EXE  | EXE                      | 0                               |

| EXE  | EXE                      | ALL                             |

| EXE  | EXE                      | 0                               |

|      | EXE<br>EXE<br>EXE<br>EXE | EXE EXE EXE EXE EXE EXE EXE EXE |

のプログラムを実行した 提合の結里

| 20 ロ の 加 木 |     |      |      |        |  |  |

|------------|-----|------|------|--------|--|--|

| 命令         | PE1 | PE 2 | PE3  | JF     |  |  |

| 1          | EXE | EXE  | EXE  | 0      |  |  |

| 2          | EXE | EXE  | EXE  | 0      |  |  |

| 3          | EXE | EXE  | EXE  | 0      |  |  |

| 4          | EXE | EXE  | EXE  | ANY    |  |  |

| 2          | _   | EXE  | EXE  | 0      |  |  |

| 3          | _   | EXE  | EXE  | 0      |  |  |

| 4          | _   | EXE  | EXE  | ANY    |  |  |

| 2          | _   | _    | EXE  | 0      |  |  |

| 3          | _   | _    | EXE  | 0      |  |  |

| 4          | _   | _    | EXE  | 0      |  |  |

| 5          | EXE | EXE  | EXE  | 0      |  |  |

| I          |     |      | L /\ | 1.1.14 |  |  |

(1)は分岐条件3を PE1 が満 たし PE2 が満たさなかった場合で 表 3 PE1,PE2,PE3で図 4 ある . この時 , CP はすべての命令 を送らなければいけないので通常 の SIMD 型マシンと同等の動作と なる.表3(2)は分岐条件3を PE1,PE2 共に満たした場合であ る.この場合4から6までの命令 はどれも実行しないので CP は全 体分岐で避ければよい.表3(3)は 逆に PE1,PE2 共に分岐条件3を 満たさない場合である.この場合 7から8までの命令はどれも実行 しないので CP は全体分岐で避け ればよい. つまり前方分岐の際,

新しく考えた分岐機構では表3(2)(3)のような場合,通 常より最適な動作が可能となる.後方分岐の場合は表4 のように,分岐の必要な PE がある限りその場で全体分 岐をおこなう.表4の場合,1回目の分岐 PE1が条件 を満たし,2回目でPE2が3回目ですべてのPEが条件 を満たし,後方分岐のループを抜けるという動作である.

## 5.まとめ

SIMD 型マシンの分岐機構を強化し高速で柔軟な処理 が可能なプロセッサの開発を行った.今後20万ゲート FPGAに8台程度のプロセッサを搭載することを目標に, VHDL による設計を進める予定である.

#### 参考文献

[1]Takahashi Yoshizo,et al , "An Enhancement of SIMD Machine for Executing SPMD Programs", ParallelComputing:Fundamentals,Applications and New Directions, North-Holland, pp. 203-206, 1997 [2]W.Daniel Hillis(喜連川優訳) , " コネクションマシ ン", パーソナルメディア, pp.24-26, 1990