C-035

# 巡回セールスマン問題を対象とする遺伝的アルゴリズムの FPGA 上への実装 Design and implementation of Genetic Algorithm for Traveling Salesman Problem on FPGA

柴田 首樹草 村田 佳洋 安本 慶一 橘 達弘 † 伊藤 実† Tatsuhiro Tachibana Yoshihiro Murata Naoki Shibata Keiichi Yasumoto Minoru Ito

## まえがき

近年,組合せ最適化問題を解くための手法(以降,組 合せ最適化手法)を FPGA 上に実装するための研究が行 なわれている [1][2] . FPGA 上に最適化手法を実装する ことで, PC より安価で,消費電力の少ない携帯端末や 組込みシステムで組合せ最適化問題の解を求めることが できる.組合せ最適化手法の1つに遺伝的アルゴリズム (GA) がある. GA は, 生命の進化を模倣しており, 交叉, 突然変異,評価,選択等の操作を用いて,解候補を進化 させる手法である.我々の研究グループでは,観光を目 的としてさまざまな制約のもとで、複数の目的地を効率 良く巡回する経路を GA を用いて計算するシステムを設 計・開発している [3]. GA を FPGA 上に実装すること で,携帯端末での巡回経路探索および案内が可能となる. 本稿では,経路探索問題の1つである巡回セールスマ ン問題 (TSP) を対象とした GA を FPGA 上に実装する. GA を FPGA 上に実装する研究には,以下に示すもの がある. Aporntewan らは親となる個体の染色体を確率的 に作成する Compact Genetic Algorithm を用いて one-max 問題に適用している [1] . Graham らは splash2 と呼ばれ

るボード上の 4 つの FPGA に TSP を対象とする GA の 実装を行なっている.この実装されたGAの計算速度は 125MHz HP PA-RISC workstation の計算速度の最大約 11 倍速いことが示されている[2].

我々は,実用規模のTSP問題を単一のFPGA上に収ま るように実装することと,実装するFPGAの回路規模に 合わせて回路の並列化が行なえるスケーラビリティを持 たせた設計を行なうことも目的とする.本稿では,TSP を対象とする GA を単一の FPGA 上に実装することを目 指し,回路規模を抑えつつ,計算速度が維持できる設計 を行なう.そのため我々は,世代交代モデルの1つであ る Minimal Generation Gap(MGG) モデルを用いる.また, 交叉方法として,アルゴリズムが比較的簡単な部分写像 交叉 (PMX)[4] を用いる.これらの手法を用いて都市数 51 の TSP を実装した結果,回路サイズが 5117LE,必要 メモリ量が 79872bit となり, Cyclone EP1C12(US\$35[5]) に実装可能であることを確認した.計算速度は,1サイク ル辺り約 1.67us であり , 同アルゴリズムをソフトウェア で実行したもの (Pentium 4 2.4 GHz, 計算時間約 1.59us) と ほぼ同等の性能を示した.消費電力は Pentium 4(2.4GHz) が 57.8W[6] であるに対し, 497.10mW であり, ソフト ウェアと比較して少ないことを示した.

## 遺伝的アルゴリズム (GA)

GA は複数の解候補を表す個体を用いることで、解を 求める手法である.この個体には解候補を符号化した染

色体 (chromosome) と個体がどれだけ良い解であるかを 示している適応度 (fitness) が含まれている.

GAは,個体群から次の世代(generation)を形成する子 の個体を生成する.その際,個体群より親となる2つの 個体を取り出す.そして取り出された2つの親の個体に 交叉 (crossover) を行ない、2つの子となる個体の染色体 を生成する . そして生成された子の個体の染色体に突然 変異 (mutation) を行なう . そして生成された個体の適応 度を調べるための操作である評価 (evaluation) を行なう. これらの操作を複数回くり返し,次の世代の個体群の候 補となる個体群を生成する.そして,与えられた適応度 より,その候補となる個体群の中から次の世代の個体群 を選ぶ.この操作を選択 (selection) と呼ぶ.これらの操 作をくり返すことで個体群を進化させ,解を求める.

#### 実装

本稿では,単一のFPGAで収まるGAを実装するため に回路規模を抑えることと,FPGA の回路規模に合わせ て GA の各操作の並列化の度合いを決定することの 2 点 を重視する.そのため,GA の世代交代モデルに MGG モデルを用いて回路の設計を行なう. MGG モデルの動 作を以下に示す. はじめに個体群より親となる個体を 2 つ取り出す.これらの親に交叉,突然変異を行ない,新 しい子の染色体を複数個生成する.生成した子の染色体 を評価する.そして選択を行なう.この選択は生成した 子と2つの親の中から最も優れた適応度を持つ個体を2 つとり出し,個体群の2つの親と入れかえる.MGG モ デルは通常の世代交代モデルとは異なり , 生成された次 世代の個体群の候補を確保する必要が無いため,回路が 簡単化できる.

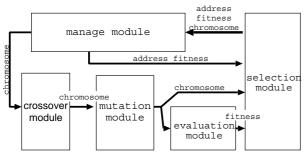

通常の交叉は,2つの個体の染色体より2つの個体の 染色体を生成する.この場合,1つの交叉を行なう回路 に対し,突然変異,評価を2回ずつ行なう回路が必要と なる.本稿では回路規模削減のために交叉は2つの個体 より1つの個体を生成することとした.以上で述べた操 作を行なう回路を図1に示す. なお GA で必要となる乱 数は , M 系列乱数を用いて作成している .

図1の回路について説明する.管理モジュール(manage module) は, FPGAの内部メモリに保持されている個体 群の情報を管理する.管理モジュールはランダムに選 択した2つの個体の染色体を親として交叉モジュール (crossover module) に送信する. その際, 管理モジュール は選択モジュール (selection module) に 2 つの親の適応度 とメモリ上のアドレスを送信する.また,管理モジュー ルは選択モジュールよりアドレス,適応度,染色体を受 けとりメモリに記録する.管理モジュールはデータの送 信を 52 クロック, 受信を 51 クロックで行なう.

交叉モジュールは,管理モジュールより受信した2つ

<sup>†</sup>奈良先端科学技術大学院大学 情報科学研究科

<sup>‡</sup>滋賀大学 経済学部

図 1: 概要図

の染色体を用いて交叉を行ない新しい子となる染色体を1 つ生成するモジュールである.そして子の染色体を突然変異モジュール (mutation module) に送信する.この際,交叉として部分写像交叉 (PMX)[4] を用いる.PMX は染色体の連続している部分を他の染色体の同じ位置で置き換える.その時,新たに生成された染色体が表わす解候補が,解として不適切とならないように調整する.交叉モジュールで必要となるクロック数は 1+3n である.n は交叉を行なう時に置き換える範囲を示す.この範囲は 2 つの乱数の差の絶対値である.

突然変異モジュールは受信した子の染色体に突然変異を行ない,評価モジュール (evaluation module) と選択モジュールに子の染色体を送信するモジュールである.この時,突然変異には2都市交換を用いる.

評価モジュールは,受信した子の染色体の評価を行ない適応度を選択モジュールに送信するモジュールである.評価モジュールでは,FPGAの内部メモリに評価用のテーブルを保持している.その評価用のテーブルを用いて各都市間の適応度を総和し,出力する.突然変異モジュールと評価モジュールはシーケンシャルに処理を行なっており,合わせて58クロックで処理を行なえる.

選択モジュールでは、はじめに管理モジュールより受信した2つの親のうち、適応度が劣っている親(aとする)のアドレスとその適応度を記録する.そして記録した適応度と突然変異モジュールより受信した子(bとする)の適応度を比較する.その結果、bの適応度が、aの適応度より優れている場合、個体群の更新を行なうためにaのアドレスとbの染色体と適応度を管理モジュールに送信する.逆にbの適応度がaの適応度より劣っている場合、選択モジュールは、管理モジュールに更新するデータが無いことを通知する.選択モジュールは,他のモジュールとは異なり用いる各データの受信するタイミングが異なる.この回路では、評価モジュールより適応度を受信した時に、全てのデータがそろう.全てのデータがそろうと1クロックで比較を行ない、結果を送信する.

この回路で,個体群の更新が発生する際に交叉,突然変異,評価,選択を行なうためには,トータル 162+3n クロックが必要となる.この内,管理モジュールでデータの送受信にかかるクロック数は 103 クロックであり,ここがボトルネックとなっている.このボトルネックの解消については,今後の課題である.

### **4.** 結果・考察

51 都市の TSP を提案手法により VHDL を用いて記述 し, Quartus II を用いて論理合成を行なった. 実装の結果, サイズは 5117LE, 必要メモリは 79872bit で,最大動作 周波数は 140MHz となった.これは Altera 社の Cyclone デバイスの EP1C12 への実装が可能である.

また, FPGA 上に実装した GA の計算速度を調べる ためにソフトウェアとして実装した同じアルゴリズムの GAとの実行時間の比較を行なった . FPGA の実行時間は Quartus II のシミュレーションを用いて計測を行なった. 比較対象としては CPU が Pentium 4(2.4GHz), メモリが 256MByte を登載している PC を用いた、性能の比較に は1個体に対する交叉,突然変異,評価,選択の一連の 操作にかかる時間の平均値を用いた、結果はソフトウェ アは約  $1.59\mu s$  , FPGA は約  $1.67\mu s$  の計算時間を要した . 以上より, 我々が設計した GA は, Pentium 4(2.4GHz) と ほぼ同等の計算速度を達成することがわかった、また、 FPGA(EP1C12) の価格は US\$35[5] である.消費電力で は, Pentium4(2.4GHz) が 57.8W[6] に対して, 設計した GA は 497.10mW であった.提案手法は,最適化問題を 解く,低コストかつ低消費電力な回路を実現する上で有 用であることが確認できた.

#### 5. まとめ

本稿では、単一の FPGA 上に TSP を対象とする GA を設計する手法を提案した、実験の結果、Pentium 4(2.4GHz) とほぼ同等の計算速度をより安価かつ低消費 電力で実現可能なことを示した。

今後の課題として,以下のことが挙げられる.1つ目はボトルネックの解消と回路のパイプライン処理による計算速度の向上である.2つ目は,FPGAのサイズに合わせて適切な回路の設計を行なうことであり,3つ目は与えられたパラメタに応じて適切な回路を示すVHDL記述を自動的に生成するシステムを構築することである.

#### 参考文献

- [1] Chatchawit Aporntewan and Prabhas Chongstitvatana, A Hardware Implementation of the Compact Genetic Algorithm, Proc. of the 2001 Congress on Evolutionary Computation, 624–629, 2001.

- [2] Paul Graham and Brent Nelson , A Hardware Genetic Algorithm for the Travelling Salesman Problem on SPLASH 2 , Field-Programmable Logic and Applications , 352–361 , 1995 .

- [3] Atsushi Maruyama , Naoki Shibatay , Yoshihiro Murata , Keiichi Yasumoto and Minoru Ito , P-TOUR: A PERSONAL NAVIGATION SYSTEM FOR TOURISM , 11th World Congress on ITS , NAGOYA , 2004 .

- [4] 北野宏明,遺伝的アルゴリズム1,50-51,産業図書株式会社,1993.

- [5] Cyclone 製品概要, http://www.altera.co.jp/literature/ wp/wp cyc backgrounder.pdf.

- [6] Processor Spec Finder ,

http://processorfinder.intel.com/

scripts/default.asp.