## C-004

# LSI 機能テスト向けプロセッサの開発 Development of the processor for LSI functional test

吉成 朝雄† 荻原 帆斗† Tomokatsu Yoshinari Hokuto Ogihara 松埜 智† 浅川 毅† Satoshi Matsuno Takeshi Asakawa

## 1. まえがき

半導体設計と製造技術の進歩とともに, LSI の高速化が続い ている、それに伴い LSI テスタにはより一層の高速化が要求 されている。しかし、LSI テスタは非常に高価なため、LSI の高速化とともに容易に買い換えるのは困難であり、LSI テ スタ導入に伴う費用は、製造時の検査や品質検査を行うため のテストコストの増加の原因の1つとなっている. 同様に LSI を使用するアセンブリメーカやボードメーカにおいては, 受 け入れテストの課題にもなっている. これら, テストコスト の増加を抑えるための研究が行われている. 既存の LSI テス タを用いて高速テストを行う手法として, CUT の内部にテス ト回路を組込む BIST (Built-In Self-Test )技術と, CUT と LSI テスタの間にテスト機能を構築する BOST ( Built-Out Self-Test)技術がある. 例えば、BIST にオンチップの PLL を組 み込み, ASIC (application specific integrated circuit) 間の高速 インターフェース回路を at-speed テストで実現する方法 [1] やブロック毎にアナログ設計用と論理回路設計用のスキャン パス回路を挿入し、実時間で高速光通信向けのアナログ・デ ジタル混在回路を検査する BOST 手法が提案されている[2]. また、TEG (test element group)を用いて高速で動作する入出 カバッファをテスタと CUT 間の BOST として構成し, 高速に メモリマクロセルを検査する方法も提案されている[3]. 他の テストコスト削減手法として, 特定の対象に特化したテスト 手法が提案されている. パソコン向け DDR3 メモリモジュー ルのテストや評価向けに、DDR3 メモリ検査に特化した命令 を備えるプロセッサを FPGA 上に構成し、LSI テスタを用い ずに高速にテストを行う手法 [4]やフラッシュメモリをテス ト対象とする低コストの FPGA による基板再構成テスタが提 案されている[5]. これらを背景に、我々は LSI の受け入れテ ストに多く用いられる機能テストに着目し、パターン信号タ イミングの切り替えをサイクル単位で行える高速プロセッサ のアーキテクチャを提案する. 本論では、アーキテクチャの 概要と FPGA への実装評価について報告する.

## 2. LSI テスタによる機能テスト

## 2.1. LSI テスタのテスト手法

LSI テスタのテスト方法には主に DC テスト, AC テスト, 機能テストなどがある. DC テストでは, 電圧値, 電流値などの DC 項目に関するテストを行い, AC テストでは, 信号伝搬遅延時間などの AC 項目のテストを行う. また, 機能テストでは, LSI に作りこまれた論理機能が正しく動作している事を検査する. 以下, LSI テスタを用いた機能テストについて示す.

## 2.2. LSI テスタの概要

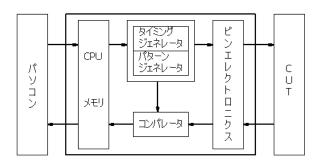

LSI テスタの基本構成例を図 2.1 に示す. パソコンなどの端

†東海大学 大学院 工学研究科 〒259-1292 神奈川県平塚 市北金目 4-1-1 末よりテストプログラムを LSI テスタに入力する. LSI テスタはテストプログラムに従いタイミングジェネレータ, パターンジェネレータ, ピンエレクトロニクスを設定し, テストプログラムのテストパターンに従って出力信号を CUT に印加する. CUT からの応答値と期待値とをコンパレータにより照合する. CUT との信号のやりとりはピンエレクトロニクスを介して行われる.

図 2.1 LSI テスタの基本構成例

#### 2.3. テストプログラムと波形の関係

テストプログラムは、テストパターン設定部と特性設定部で構成されている. 先ず、テストパターン設定部のプログラム例を図 2.2 に示す.

MAIN.

(NOP/T0!10L) //1 回目印加するパターン

(NOP/T0!01L) //2 回目印加するパターン

(NOP/T0!11H) //3 回目印加するパターン

(STOP/T0!10L) //4 回目印加するパターン

MAINEND.

図 2.2 テストパターン設定部プログラム例

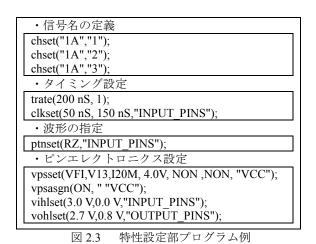

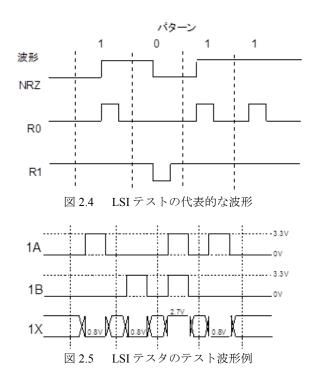

「テストパターン設定部」には出力ピンの論理値パターンとコンパレータの期待値を記述する。例えば、出力パターンは1または0を、期待値はHまたはLと記述する。次に特性設定部のプログラム例を図2.3に示す。特性設定部における「信号名の定義」ではテストプログラム内で使用する信号名を定義し、「タイミング設定」ではLSIテストの1周期の長さとパターンの変化するタイミングを設定する。「波形の指定」では出力波形タイプを指定し、「ピンエレクトロニクス設定」では入出力種および出力ピンの電気的特性と入力ピンの判定しきい値を設定する。次にLSIテスタの代表的な出力波形タイプを図2.4に示す。

## • NRZ ( non-return zero )

NRZ はリセットを行なわず、次の周期まで出力論理値を維持する.

### • R0 ( return 0 )

R0 はリセット時に信号を 0 にする. そのため, 周期の開始

と終わりで必ず0になる.

#### • R1 ( return 1 )

R1 はリセット時に信号を1にする. R0 と反対に周期の開始と終わりに必ず1になる.

図2.2のテストパターン部と図2.3の特性設定部の記述内容より作成される出力信号および期待値は図2.5のようになる.

表 3.1 プロセッサの命令表

| 命令種                    | 命令コード | 機能                                |

|------------------------|-------|-----------------------------------|

| PIO                    | 0     | I/O 部を入力設定にする                     |

| (入出力選択)                | 1     | I/O 部を出力設定にする                     |

| WSA<br>(第 1 出力論理値)     | 01    | 出力論理値 0                           |

| WSB<br>(第 2 出力論理値)     | 10    | 出力論理値 1                           |

|                        | 000   | クロック生成部で作成されたクロックのうち1番目のクロックを選択する |

|                        | 001   | クロック生成部で作成されたクロックのうち2番目のクロックを選択する |

| CCA                    | 010   | クロック生成部で作成されたクロックのうち3番目のクロックを選択する |

| (第 1 出力変化タイミング)<br>CCB | 011   | クロック生成部で作成されたクロックのうち4番目のクロックを選択する |

| (第 2 出力変化タイミング)<br>PC  | 100   | クロック生成部で作成されたクロックのうち5番目のクロックを選択する |

| (照合タイミング)              | 101   | クロック生成部で作成されたクロックのうち6番目のクロックを選択する |

|                        | 110   | クロック生成部で作成されたクロックのうち7番目のクロックを選択する |

|                        | 111   | クロック生成部で作成されたクロックのうち8番目のクロックを選択する |

|                        | 00    | ドント・ケア (照合結果を無視する)                |

| LV                     | 01    | n .                               |

| (期待値)                  | 10    | 期待値を Low(0)に設定する                  |

|                        | 11    | 期待値を Hi(1)に設定する                   |

## 3. プロセッサの概要

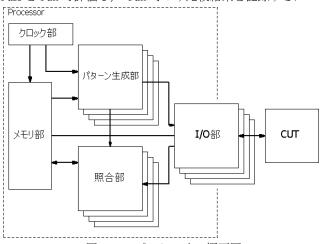

本研究では、タイミング的に自由度のあるパターンを高速に印加出来る LSI 機能テスト向けプロセッサのアーキテクチャの検討を行った。テスト中における命令はすべて 1 クロックで実行し、位相がずれた複数の遅延クロックを使うことで同一動作周波数の標準的なプロセッサと比べ高速に動作する

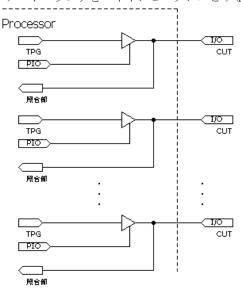

ことを可能とする. 高速プロセッサの概要を図 3.1 に示す. プロセッサは, 位相の異なる遅延クロックを生成するクロック部, CUT に印加するパターンの生成及び測定タイミングを生成するパターン生成部, プロセッサの命令を蓄えるメモリ部, 全てのピンにそれぞれリアルタイムな入出力設定が可能な I/O 部, CUT からの応答値と期待値とを比較する照合部で構成されている. このうち, パターン生成部, I/O 部, 照合部

は I/O ピン単位で構成しているため LSI の規模に対してモジュール数を変更することで対応することができる. テスト実行の際,メモリ部に書き込まれた命令を用いて各部の設定が行われ動作する. パターン生成部では、クロック部で生成されたタイミングを使用してパターン生成を行い、CUT への印加パターンを I/O 部に、測定タイミングを照合部に送る. I/O 部では、出力設定された I/O のみにパターン生成部からのテストパターンを出力する. 照合部では、パターン生成部で生成された測定タイミングを用いて I/O 部より送られた CUT の応答値と期待値とを比較する. プロセッサは、テスト結果をPass と Fail で評価し、Fail 時のみ比較結果を記録する.

図3.1 プロセッサの概要図

プロセッサの命令表を表 3.1 に示す.表 3.1 では遅延クロック数が 8 の場合を想定している. PIO は I/O の入出力を決定する. WSA と WSB は出力論理値を決定し, CCA と CCB を組み合わせて CUT への印加パターンを生成する. 出力論理値は, ハイインピーダンスなどの拡張を考慮して 2bit で構成している. PC は照合タイミングを決定する. いずれもタイミングの分解能はクロック部で生成される遅延クロック数に依存する. LV は期待値を設定し,上位ビットが 0 の場合は,ドント・ケアとし,1 の場合は下位ビットの値とする. これらの命令はサイクルごとに記述する.命令構成及び命令長を表 3.2 に示す.

表 3.2 プロセッサの命令構成(bit 数)

| PIO | WSA        | WSB        | CCA            | CCB            | PC             | LV         |

|-----|------------|------------|----------------|----------------|----------------|------------|

| n   | 2 <i>n</i> | 2 <i>n</i> | <u>nlog2 j</u> | <u>nlog2 j</u> | <u>nlog2 j</u> | 2 <i>n</i> |

表 3.2 では、I/O 数が n bit、遅延クロック数が j の場合の 1 サイクル分の命令構成を示し、命令長は  $\overline{2n+3n\log_2 j}$  で示される。例えば、I/O 数を 8、遅延クロック数を 8 とした場合は  $7 \times 8 + 3 \times 8 \log_2 8 = 56 + 72 = 128 \text{bit}$  となる。高速化や拡張性に考慮し命令を各部で並列にデコードし、機能単位に分割して扱う。

表 3.3 プロセッサ命令例(bit)

|         | 20.0  | /     | 1.14 14 12 (07 0) |         |

|---------|-------|-------|-------------------|---------|

| PIO     | WSA   | WSB   | CCA               | CCB     |

| 0 1     | dd 01 | dd 10 | ddd 001           | ddd 101 |

| PC      | LV    |       |                   |         |

| 100 ddd | 01 d0 |       |                   |         |

I/O 数が 2 つの場合の 1 サイクル分の命令例を表 3.3 に示す.

表 3.3 の「d」はドント・ケアを示す. 命令は PIO から LV までの機能ごとに I/O 数分記述する.

## 4. プロセッサの構成要素

### 4.1. クロック部

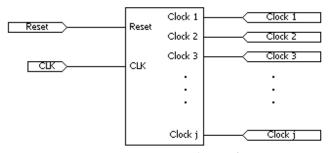

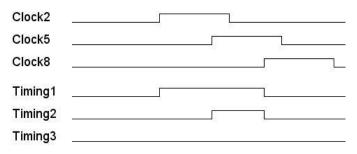

図 4.1 クロック部の構成

クロック部の構成を図 4.1 に示す. クロック部では,基準クロックとリセット信号を入力し  $Clock\ 1 \sim Clock\ j$  までの j 個の位相が異なる遅延クロックを生成する. このクロック数に応じて細かいタイミング設定が可能となり,簡易的な AC テスト項目も行うことが可能である.

## 4.2. パターン生成部

パターン生成部は、TPG (Test Pattern Generator), と PTG (Probe Timing Generator)の 2 つが、I/O ピン単位で構成されている.ここでは、1 つの I/O 部分について説明を行う.

## (1) TPG

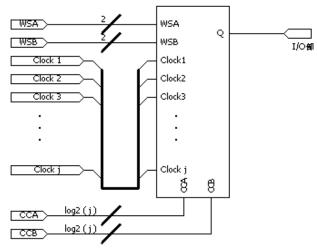

図 4.2 TPG の構成

表 4.1 プロセッサパターン生成部分命令

| Pattern | WSA | WSB | CCA | CCB |

|---------|-----|-----|-----|-----|

| 1       | 10  | 01  | 001 | 011 |

| 2       | 10  | 01  | 010 | 110 |

| 3       | 10  | 01  | 000 | 111 |

| 4       | 10  | 10  | 101 | 111 |

| 5       | 10  | 10  | 000 | 111 |

| 6       | 01  | 10  | 010 | 111 |

| 7       | 01  | 10  | 000 | 100 |

| 8       | 01  | 01  | 011 | 111 |

| 9       | 01  | 01  | 000 | 111 |

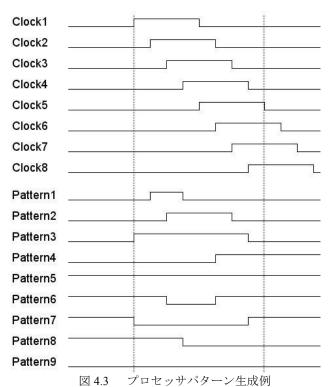

TPG の構成を図 4.2 に示す. TPG では、j 個の遅延クロックと出力変化タイミング CCA, CCB 及び出力論理値 WSA, WSB を入力して出力パターンを生成する. CCA の選択した遅延クロックの立ち上がりエッジのタイミングで WSA が出力され、CCB の選択した遅延クロックの立ち上がりエッジで WSB が出力される. 次に TPG で使用する主な部分命令を表4.1 に、表4.1 に対応する生成パターンを図 4.3 に示す. 例えば、Pattern 1 の場合、CCA の選択した Clock 2 の立ち上がりで WSA の出力論理値 1 を出力し、CCB が選択した Clock 4で WSB の出力論理値 0 を出力する. このように、TPG では2つの遅延クロックを使い、自由度の高いパターンを生成する. TPG で生成されたパターンは、I/O 部を経由して CUT に印加される.

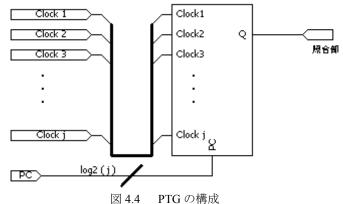

## (2) PTG

PTG の構成を図 4.4 に示す. PTG では, j 個の遅延クロックと照合タイミング PC を入力して, 遅延クロックから照合タイミングを選択する. PTG で使用する主な部分命令を表 4.2 に, 表 4.2 に対応する生成タイミングを図 4.5 に示す. 例えば, Timing 1 の場合, PC の選択した Clock 2 の立ち上がりを照合タイミングとして用いる.

表42 プロセッサ測定タイミング生成部分命令

| Timing | PC  |

|--------|-----|

| 1      | 001 |

| 2      | 100 |

| 3      | 111 |

図 4.5 プロセッサタイミング生成例

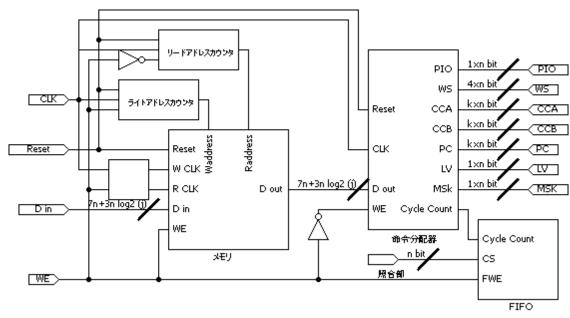

#### 4.3. メモリ部

図 4.6 に示すメモリ部は、プロセッサへ与える命令を蓄えるデュアルポートメモリ、命令分配器からのサイクル番号と照合結果を蓄える FIFO、デュアルポートメモリの命令を各部に分割して与える命令分配器によって構成されている。デュアルポートメモリの機能を表 4.3 に示す.

表 4.3 デュアルポートメモリの機能

| ,                  | 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |

|--------------------|-----------------------------------------|

| 信号名                | 機能                                      |

| Reset (reset)      | 1: メモリのリセット                             |

| WCLK (write clock) | メモリ書き込み時のクロック                           |

| RCLK (read clock)  | メモリ読み込み時のクロック                           |

| WE (ita anal-la)   | 0: メモリの書き込み許可                           |

| WE (write enable)  | 1: メモリの読み込み許可                           |

| D-in (data-in)     | メモリへの入力                                 |

| D-out (data-out)   | メモリからの出力                                |

## 4.4. I/O 部

図 4.7 の I/O 部は、トライステートバッファで構成され、PIO が 1 の場合は、TPG からの出力を印加し、PIO が 0 の場合は、トライステートバッファをハイインピーダンスとする. また、

図 4.7 I/O 部の構成

図 4.6 メインメモリの構成

CUT の応答値及び出力論理値は、PIO の設定値に依存せず 照合部に送られるため、プロセッサのループバックテストに 用いる事も可能である.

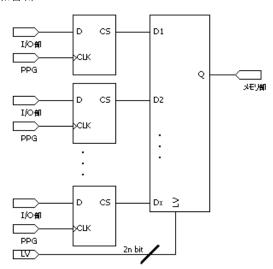

#### 4.5. 照合部

照合部の構成 図 48

照合部の構成を図 4.8 に示す. 照合部では, I/O 毎に PPG の 立ち上がりタイミングで CUT からの応答値または出力論理 値を保持する.保持された値は,PPG の立ち下がりのタイミ ングで期待値 LV と比較され, 0(Pass)か 1(Fail)で評価される. 照合結果が Fail の場合のみ I/O 箇所がサイクル番号とともに メモリ部に保存される.

## プロセッサの評価

#### 5.1. FPGA への実装

検討したアーキテクチャに基づき設計したプロセッサを FPGA へ実装し評価を行った. 開発環境は FPGA 開発ツール である Xilinx 社の ISE Design Tools 14.5 を使用し, デバイスは Xilinx 社の XC3S700AN を使用した. 3 章に示すモジュールご とに分割して設計を行った. プロセッサは I/O 数 n を 8, 遅延 クロック数jを8として設計した. 論理合成の結果を表 5.1 に 示す.

表 5.1 論理合成結果

|       | スライス数 | スライス FF 数 | 4入力 LUT 数 |

|-------|-------|-----------|-----------|

| クロック部 | 4     | 8         | 2         |

| TPG   | 74    | 32        | 144       |

| PTG   | 116   | 193       | -         |

| I/O 部 | 5     | -         | 16        |

| メモリ部  | 299   | 170       | 528       |

| total | 393   | 326       | 883       |

### 5.2. 波形観測による評価

FPGA に実装したプロセッサの出力波形をパターンとタイ ミングに注目し、ロジック・アナライザを用いて動作の検証 を行う. ロジック・アナライザは 54620A (Hewlett-Packard 社 製, 現 Agilent 社)を用いた.

## (1) 出力パターンの評価

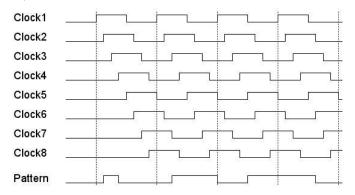

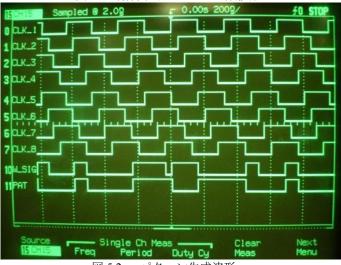

出力パターンの組み合わせに注目して RO, NRZ, R1, NRZ の順でパターン生成を行う部分命令を表 5.2 に示し、期待さ れるパターンを図 5.1 に示す. また,表 5.2 の命令を実行し, ロジック・アナライザで観測した結果を図5.2に示す.

表 5.2 プロセッサパターン生成部分命令

| Pattern | WSA | WSB | CCA | CCB |

|---------|-----|-----|-----|-----|

| 1       | 10  | 01  | 001 | 011 |

| 2       | 10  | 00  | 010 | 111 |

| 3       | 01  | 10  | 000 | 100 |

| 4       | 00  | 01  | 011 | 101 |

1サイクル中に生成されるパターンは第1出力変化タイミン グ CCA と第1出力論理値 WSA, 第2出力変化タイミング CCB と第2出力論理値 WSB の組み合わせによって決定される. 図 5.2 は、 $プローブ 0 \sim 7$  が遅延クロック、プローブ 10 が 出力変化タイミング, プローブ 11 が生成されたパターンを表 す. プローブ 11 を見ると図 5.1 の Pattern と同じ波形が観測できるのが分かる.

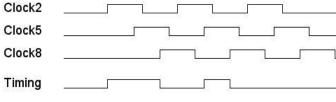

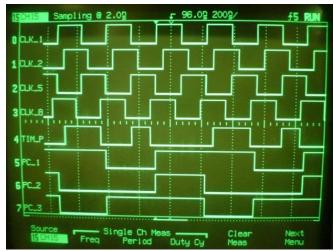

## (2) タイミングの評価

タイミングの組み合わせに注目したプログラムを表 5.3 に示し、期待するパターンを図 5.3 に示す. また、表 5.3 の命令を実行し、ロジック・アナライザで観測した結果を図 5.4 に示す.

図 5.1 期待するパターン生成波形

図 5.2 パターン生成波形

表 5.3 プロセッサ測定タイミング生成部分命令

|        | */  |

|--------|-----|

| Timing | PC  |

| 1      | 001 |

| 2      | 100 |

| 3      | 111 |

1 サイクル中に生成されるタイミングは照合タイミング PC によって決定される. 図 5.4 は、プローブ 0 ~ 3 が遅延クロック、プローブ 4 が生成されたタイミング、プローブ 5 ~ 7 が PC を表す. プローブ 4 を見ると図 5.3 の Timing と同じ波形が観測できるのが分かる. 図 5.2 より CCA、CCB、WSA、WSB の信号を用いて指定したパターンの生成が出来ている事が確認できた. さらに、図 5.4 より PC で指定したタイミングでも

図 5.3 期待するタイミング生成波形

図 5.4 タイミング生成波形

同様にプローブが立ち上がるのが確認できた.また,その他の組み合わせも観測した結果,パターン生成,タイミング生成ともに全ての組み合わせで指定した波形を生成できることが確認できた.

#### 6. かすび

本研究では、LSI機能テスト向け高速プロセッサのアーキテクチャを検討し、プロセッサを FPGA に実装して評価を行った.評価の結果、パターン信号タイミングの切り替えをサイクル単位で行える事を波形観測により確認した.また、測定のタイミングに関しても遅延クロックから任意のクロックを選択し測定タイミングが生成できることを確認した.今後の展望として、テストプログラムを簡単に作成できるコンパイラの開発や大規模回路を用いた評価を行っていきたい.

#### 謝辞

本研究は、一部、JSPS 科研費 23500068 の援助を受けている.

#### 参考文献

- [1] 横田駿彦, "オンチップ PLL を用いた LSSD 高速スキャンテストとソースシンクロナス DDR インターフェイスへの応用", 電子情報通信学会技術研究報告. DC, ディペンダブルコンピューティング 106(391), pp. 39-44, Nov, 2006.

- [2] 平野進,小林竜也,堤恒次,山岸圭太郎,峯岸孝行, "高速光通信向けアナデジ混在大規模 LSI テスト設計," 電 子情報通信学会総合大会講演論文集 2011年\_エレクトロニクス(2), pp. S-28, Feb, 2011.

- [3] 柴田慎太郎, 石原隆子, "LSI テスタによる高速マイクロセルの一試験法," 電子情報通信学会技術研究報告.

- ED, 電子デバイス 95(117), pp. 31-38, Jun, 1995. [4] 浅川毅, 松埜智, 土屋秀和, 関達也, 熊澤 慎一, "デ

- スト命令に基づく DDR3 メモリモジュールテスタの開発," 電子情報通信学会論文誌. D, 情報・システム J95-D(4), pp. 928-939, Apr, 2012 年.

- [5] 佐藤正幸, 大塚信行, 武藤治, 新井雅之, 福本聡, 岩崎一彦, 上原孝二, 志水勲, 間明田治佳, "低消費電力基板型再構成テスタの開発,"信学論(D-I), Vol. J88-D-I, No. 6, pp. 1065 1075, June 2005.