### C-004

動的部分再構成技術を用いた専用計算機システムの開発 Special Purpose Computer System using Partial Reconfiguration Technology

廣田 祐輔\*

佐藤 紘将\*

山本 洋太\*

増田 信之\*

Yusuke Hirota

Hiromasa Satou

Yota Yamamoto

Nobuyuki Masuda

## まえがき

近年,生命科学,天文学分野など様々な科学技術分野でシミュレーションが行われており,研究開発のコスト削減や時間短縮のために計算処理の高速化が求められている。この問題を解決するために,本研究室ではFPGA(Field Programmable Gate Array) 搭載評価ボードを用いて,計算処理を高速に行う専用計算機の開発を行っている[1]-[4]. FPGA は内部回路の書き換えが自由に行えるため,回路を書き換えることで様々な数値計算に対応できる。しかし,FPGA内の回路を書き換えるには,一般的には一度,計算機システムの電源を切る必要がある。そのため,計算システムの切り替えにはかなりの時間が必要となる。

現在市販されている一部の FPGA には Partial Reconfiguration 技術が実装されている。この技術は、FPGA 内の回路全体ではなく、予め決めておいた領域だけを書き換えることができる。そのため、FPGA 内全ての回路を書き換える場合に比べて、書き換え時間を抑えることが出来る。この技術を応用することで、計算機システムの電源を切らずに FPGA 内の必要な回路を変更することが出来る。

本研究では、Partial Reconfiguration による回路の書き込み時間を計測し、計算機システムの変更にかかる時間を検証した.

# 2. Partial Reconfiguration

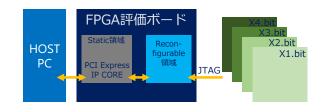

Partial Reconfiguration は、Partial BIT File を書き 込むことで、動作中のロジックブロックを動的に変更で き、そのほかロジックは中断せずにそのまま保持でき る. Full BIT File で FPGA をコンフィギュレーション した後に、Partial BIT File を書き込むと、デバイスの リコンフィグレーションされない部分で実行されている アプリケーションに影響を与えることなく, FPGA の Reconfigurable 領域を変更することが可能である. 図 1 に Partial Reconfiguration の概略図を示した. 図1に 示すように、Reconfigurable 領域に X1~X4 いずれかの Partial BIT File を書き込むことで、回路内の一部が書 き換わる. Partial Reconfiguration 技術を用いることで, ロジックブロックの一部を再構成することが出来る. そ のため、FPGA 内全ての回路を書き換える場合に比べ て,書き換え時間を抑えることが出来る.この技術を 応用すると計算機システムの電源を切らずに短時間で FPGA 内の必要な回路を変更することが出来る. また, 1つの FPGA で複数のアプリケーションを実行できるた め, ハードウェアの削減が実現し, デバイス数の削減, 消費電力の削減、ボードの小規模化、および全体的なコ ストの削減が可能となる.

図 1: Partial Reconfiguration の概略図

## 3. 実験結果

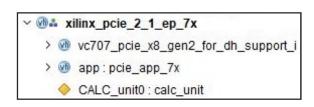

本研究では、3次元計測システムのためのデジタルホログラフィ専用計算機に Partial Reconfiguration を実装した[2]. 本計算回路は図2に示した通り、PCI Express回路とホログラムの再生像を計算する回路から成る.

図 2: 階層デザイン

図3のように、FPGA上に、PCI Express と計算部を 制御するモジュール、ホログラム処理に必要な IP コア が含まれている Calc Unit Module を書き込むため、そ れぞれ Static 領域、Reconfigurable 領域を設定した.

図 3: 専用計算機システム

さらに、PCI Express は Static Module として最上位デザインの一部として設定し、Calc Unit Module は Reconfigurable Module として設定した。Reconfigurable 領域に Reconfigurable Module を書き込むことで、システム全体の電源を切らずに、動的部分再構成が可能となる。

<sup>\*</sup>東京理科大学基礎工学部

ここでは、Full BIT File、Partial BIT File の書き込みにかかった時間を比較した.

#### 3.1 実験環境

専用計算機には、Xilinx 社製の FPGA 評価ボード VC707 を使用した (搭載 FPGA Virtex-7 XC7VX485T-2FFG1761). また、回路データの作成や FPGA の動作 検証を行った環境を表 1 に示す.

表 1: ソフトウェア開発環境

| CPU       | Intel Core i7-6700K 4.00 GHz |

|-----------|------------------------------|

| メモリ       | 16 GB (8GB × 2)              |

| OS        | CentOS7.5.1804               |

| FPGA 開発環境 | Vivado 2017.4                |

#### 3.2 部分再構成の結果

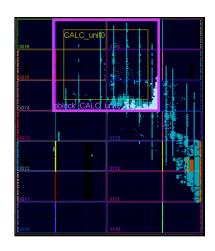

図4に計算回路合成後のフロアプランを示した. 紫色の枠で囲われている部分が Reconfigurable 領域, それ以外の領域が Static 領域である.

図 4: フロアプラン

作成した回路情報 (BIT File) のサイズを表 2 に示す. Full BIT File には、PCI Express IP コアと Calc Unit Module が含まれている.一方、Partial BIT File には、Calc Unit Module のみが含まれている.これらのビッ

表 2: BIT ファイルサイズ

| Full BIT File[KB] | Partial BIT File[KB] |

|-------------------|----------------------|

| 5,158             | 3,017                |

トファイルを FPGA への書き込みにかかった時間を表3に示す.

Partial Reconfiguration 技術を利用して Reconfigurable 領域に Partial BIT File 化した計算回路を書き

表 3: FPGA 書き込み時間

| Full BIT File[s] | Partial BIT File[s] |

|------------------|---------------------|

| 3.41             | 1.83                |

込むのにかかる時間は、Full BIT File の書き込みにかかる時間に比べて約1.86 倍高速であることがわかった.また、Partial Reconfiguration 技術を導入する前後で、計算回路の動作周波数を落とさずに実装でき、計算機システムが正しく動作することを確認した.

## 4. まとめと今後の課題

本研究より、Partial Reconfiguration を使用する場合、使用しない場合に比べて約1.86倍の高速化することが確かめられた。今後は、より上位のFPGA評価ボードである VCU108 評価ボードに実装を目指す、VCU108 評価ボードに専用計算回路を実装することで、以下2点が可能となる。1つ目は、回路規模が大きくなるため複数の計算回路を実装できる。2つ目は、PCI Express 経由でFPGA内を動的部分再構成することが可能になる。Ultra-Scale デバイスでは MCAP(media configuration access port)をサポートしており、このポートを使用することで、PCI Express 経由で FPGA内を Partial Reconfiguration できるようになる。本研究では、JTAG 経由でPartial Reconfigurationを行い、BIT File 転送速度の理論値が 1,875[KB/s]と低速であったが、PCI Express 経由で行うことで、さらなる高速化が期待できる。

# 謝辞

本研究は JSPS 科研費 18K11328, の助成を受けたものです.

#### 参考文献

- [1] N. Masuda et al. Opt. Express, 14, 587-592 (2006).

- [2] 増田信之, 松田美由妃, 臼倉圭亮, 難波慎太郎, 的場 駿介, 角江崇, 下馬場 朋禄, 伊藤智義, "C-003 高速 度デジタルホログラフィのための専用計算回路の並 列化 (C 分野: ハードウェア・アーキテクチャ, 一 般論文)", 情報科学技術フォーラム講演論文集 14.1, p235-p236, 2015.

- [3] 廣田祐輔, 山形健太, 山本洋太, 山本未来呂, 南昇吾, 増田信之, "C-011 パーシャルリコンフィグレーションを用いた専用計算機システムの開発 (C 分野: ハードウェア・アーキテクチャ, 一般論文)", 情報科学技術フォーラム講演論文集, p221-p222, 2017.

- [4] 山形健太, 山本洋太, 廣田祐輔, 難波慎太郎, 増田信之, , 阿比留慎, 角江崇, 下馬場朋禄, 伊藤智義, "C-010 三次元計測システムのためのディジタルホログラフィ専用計算機の開発 (C 分野: ハードウェア・アーキテクチャ, 一般論文)", 情報科学技術フォーラム講演論文集, p219-p220, 2017.