# リアルタイム手書き文字認識の SoC 上で 実現方式の検討

# 田中 龍斗<sup>†</sup> 中西 知嘉子<sup>††</sup> † 大阪工業大学大学院情報科学研究科 † † 大阪工業大学情報科学部

## 1. はじめに

紙に記入されている手書き数字を読み取る技術は郵便番号の読み取りなど様々なところで使われている.数字の認識はディープラーニングの得意分野であり,手書き文字・数字で高い精度で実現するには,必須の技術である.しかし,ディープラーニングは演算量が多くソフトウェアでの実行には多くの時間がかかる.また,ハードウェアのみでの実装は複数の数字が任意の場所に書かれている場合を考慮すると紙から数字部分を的確に選び出す必要があり処理が複雑で回路が大きくなるだけでなく実装にも時間がかかる.

本研究では紙に書かれた数字認識処理をソフトウェアとハードウェアの両方を用いて実現する. すなわち,紙から数字を選び出す処理をソフトウェアで行い,切り取った数字の認識をハードウェアで行う. 実装にはDigilent 社の ZYBO Z7-20 で CPU の OS にはUbuntu16.04LTSを使用した.

# 2. 手法

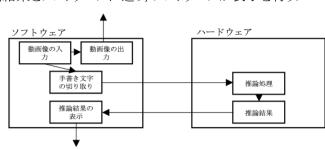

ソフトウェアで動画像の入出力を行い,手動で指定した範囲を選択し切り取りを行う. さらに,切り取られた画像を 28×28 のサイズにリサイズを行い,ハードウェアに画像を送信する.ハードウェアは推論処理を実行し推論結果をソフトウェアに送り、ソフトウェアが表示を行う.

図 1 システムの構成

推論部分の回路は Vivado HLS 2017.4 で C++の ソースコードの合成を行い HDL にしてから IP 化し、回路に組み込んだ。図 2 に C++ソースコードを HDL コードに合成した結果のリソース使用量のレポートを示す。

| Name            | _BRAM_1 | 8K  | DSP48E | FF     | LUT   |

|-----------------|---------|-----|--------|--------|-------|

| DSP             | -       |     | 5      | -      | -     |

| Expression      | -       |     | 0      | 0      | 2213  |

| FIFO            | -       |     | -      | -      | -     |

| Instance        |         | 4   | -      | 736    | 882   |

| Memory          | 1       | 55  | -      | 21     | 14    |

| Multiplexer     | -       |     | -      | -      | 608   |

| Register        |         | 0   | -      | 990    | 64    |

| Total           | 1       | 59  | 5      | 1747   | 3781  |

| Available       | 2       | 280 | 220    | 106400 | 53200 |

| Utilization (%) |         | 56  | 2      | 1      | 7     |

図 2 リソースの使用量のレポート

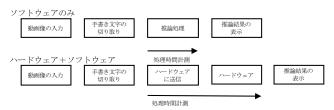

#### 3. 評価方法

ソフトウェア単体で行う手法とハードウェアとソフトウェア組み合わせた手法のそれぞれの処理時間を評価する. 手書き文字の切り取り後から推論結果が表示される前までの処理時間を10回計測し, 平均を取った.

図 3 処理時間の評価方法

精度は,0~9までの数字それぞれを10回選択し,認識を行った時の正しく推論できた回数で評価する.

## 4. 評価結果

ソフトウェア単体での処理時間は  $0.047627 \sec$  であった。また,ソフトウェアとハードウェアを組み合わせた手法での処理時間は  $0.014181 \sec$  で約 3.36 倍の性能が良くなった。また,各数字の正しく推論できた回数を表 1 に示す.

表 1 正しく推論できた回数

|      | 0 | 1  | 2 | 3   | 4 |

|------|---|----|---|-----|---|

| hard | 7 | 10 | 8 | 9   | 7 |

| soft | 8 | 10 | 8 | 10  | 8 |

|      | 5 | 6  | 7 | - R | a |

|      | 0 | 0  | - | -   | 9 |

| hard | 9 | 6  | Б | Б   | 3 |

| soft | 9 | 7  | 7 | 8   | 3 |

#### 5. 今後の展望

複数の手書き数字認識は、回路を並列化し同時に処理することによって高速化する予定である.

### 参考文献

[1] 小野雅晃「手書き数字認識用 FPGA ニューラルネットワークシステムの製作」、『トランジスタ技術』2018 年 11 月号, CQ 出版