# タイムインターリーブ ADC のための多位相クロック生成回路の研究柳部 正樹 日野 翔太 升井 義博 \*\*

† 広島工業大学 工学部 電子情報工学科

### 1. はじめに

私たちの身の回りにある電子機器には多くの Analog to Digital Converter (ADC) が使われている. 近年では高速なアナログ信号を扱うために、サンプリング速度の向上が求められている. しかし、単一の ADC のサンプリング速度を上げるには限界がある. そこで、複数のADCを並列動作させてサンプリング速度を上げるインターリーブという手法が注目を浴びている. 本稿では、インターリーブに用いる多位相クロック生成用のリング型発振器を提案する.

## 2. 課題

複数のADCを並列に使用するタイムインターリーブには以下3点の課題がある.

- サンプリング時のタイムスキュー誤差

- ・各 ADC のゲイン誤差

- ・各 ADC のオフセット誤差

ゲイン誤差とオフセット誤差に対してはデジタル補正が 他論文で提案されているため,本稿ではデジタル補正 の難しいタイムスキュー誤差を補正する回路構成を提 案する.

### 3. 提案する回路の特徴

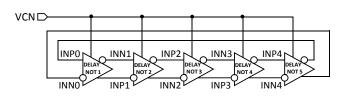

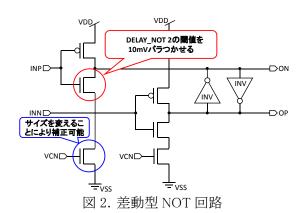

タイムインターリーブ ADC には位相差が均等でその合計が 360 度になる複数の矩形波が必要である. そこで今回提案する回路は,図1のように差動型 NOT 回路をリング状に接続するリング型発振器を使用する. リング型発振器はそれぞれのNOT回路の接続間の位相差が均等であるためひとつの回路でタイムインターリーブ ADC に使用する矩形波を作ることができる. 各 NOT 回路の構成を図 2 に示す.図 2 の VCN にかかる電圧を変えることによって発振周波数を変えることができる (30MHz~150MHz).

図 1. 多位相クロック生成回路

4. シミュレーションの結果

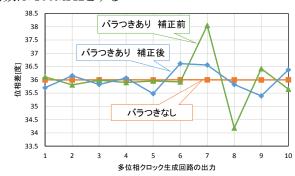

MOS トランジスタの閾値バラつきによる位相誤差を VCN が入力される MOS トランジスタのサイズを変えるこ とにより補正できることを図 3 に示す.この時の発振周 波数は 100MHzとする

図3. 各出力の位相差

### 6. むすび

本稿ではタイムインターリーブ ADC での利用を想定し、MOS トランジスタの閾値バラつきによる影響を補正できる多位相クロック生成回路を提案した. 今後はより精度の高い補正方法と補正の自動化手法に関して検討していきたい.

### 謝辞

本研究は東京大学大規模集積システム設計教育研究センター を通じケイデンス㈱,およびローム㈱の協力で行われたものである

# 参考文献

[1] 株式会社ミッシュインターナショナル: 「SP Devices 社インターリーブ技術」