# ハードウェアアクセラレータの放射線耐性

## Radiation tolerance of a hardware accelerator

寺田涼 渡邊実

Ryo Terada Minoru Watanabe

静岡大学 工学部電気電子工学科

Faculty of Engineering, Department of Electrical and Electronic Engineering, Shizuoka University

#### 1. はじめに

原子炉周辺や宇宙空間において半導体デバイスを使用する場合には、高エネルギーの放射線の影響を受ける.影響の一つにフリップフロップの値が反転したり、回路の動作が一時的におかしくなるソフトエラーがある.ソフトエラーを抑えるには回路の多重化が有効である.本稿では、多重化によるソフトエラー耐性を評価する.

## 2. 多重回路

回路の多重化とは同じ回路を複数実装して多数決回路により出力を得る方法である。三重回路ならば、同じ回路を3 つ実装しその多数決を出力とする。もし、ソフトエラーが発生して一つの回路出力が反転しても、多数決により正常値を出力できる。回路は多重化するほど冗長性が増し、ソフトエラー耐性は高くなる。

## 3. 評価回路

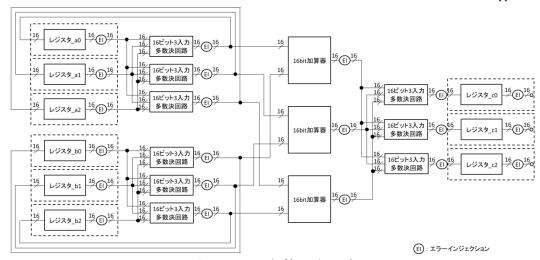

16 ビット加算回路を多重化した,三重 16 ビット加算回路と五重 16 ビット加算回路を設計した.これにエラーインジェクションを行い,多重回路のソフトエラー耐性を評価する.実装した三重 16 ビット加算回路のブロック図を図 1 に示す.回路は 16 に実装した.

## 4. 評価結果

多重化したレジスタ出力の多数決の結果がレジスタの正常値と不一致だった場合を異常として検出した.

表 1 評価条件

| 回路   | 動作周波数 | エラーインジェクション回数 |  |

|------|-------|---------------|--|

|      | (MHz) | (回/秒)         |  |

| 三重回路 | 50    | 336万          |  |

| 五重回路 | 50    | 560 万         |  |

表 2 多重 16 ビット加算回路の異常検出数

|      | 異常検出数(回/秒) |        |        |  |

|------|------------|--------|--------|--|

| 回路   | レジスタ_a     | レジスタ_b | レジスタ_c |  |

| 三重回路 | 186        | 190    | 5541   |  |

| 五重回路 | 0.10       | 0.10   | 59.03  |  |

表 1 の条件でエラーインジェクションを行った際の異常 検出回数を表 2 に示す.表 2 より五重回路の異常検出数は 三重回路と比較して,レジスタ\_a,レジスタ\_b では約 0.054%に,加算結果が書き込まれるレジスタ\_c では約 1.1%になっている.16 ビット加算回路の多重化では,五重回路 は三重回路の約 94 倍のソフトエラー耐性を持つ.

#### まとめ

三重 16 ビット加算回路と五重 16 ビット加算回路を設計し、エラーインジェクションでソフトエラー耐性を評価した。今後は、放射線を照射して評価する予定である.

## 参考文献

[1] 高江洲康太郎, 吉田 たけお, "多数決冗長系における多数決回路の高信頼化に関する一検討,"電子情報通信学会論文誌, vol.J84-D-I, no.4, pp, 378-388

図1 三重16ビット加算回路のブロック図