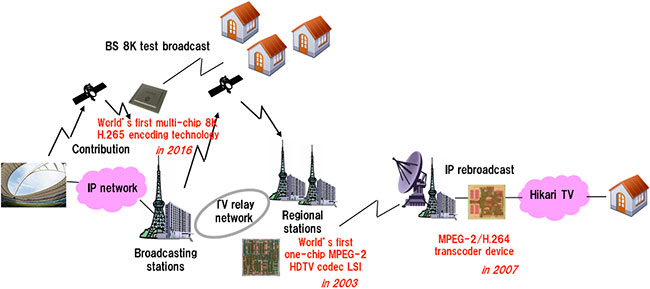

With the development of video coding technologies, digitalization of broadcast programs has been proposed in various countries and there has also arisen a demand for advanced user experience through cooperation among communication and broadcast services. The award recipients, as shown in Fig. 1, have promoted video codec LSIs and devices conforming to the video coding technologies that have progressed from MPEG-2 through H.264 and H.265, which have supported a sequence of communication/broadcast cooperation services such as development of terrestrial digital broadcasting, practical application of IP rebroadcasting, and 8K test broadcasting.

In order to launch terrestrial digital TV broadcasting in December 2003, MPEG-2 video coding LSI (VASA) was developed as a key technology for television relay networks that are used for contribution (broadcast content material transmission) supporting Japanese digital broadcasting systems. At the time, as there was no development example anywhere in the world of MPEG-2 HDTV encoding/decoding installed into one chip, this development contributed significantly to the successful introduction of terrestrial digital broadcasting in Japan in 2003. More than 10 years have elapsed since then and transition from analog to digital has progressed smoothly in Japan. In addition, it has also been widely adopted by overseas manufacturers and has contributed to the global industry in over a long period.

For H.264 video coding LSI (SARA), in order to realize IP rebroadcast services, the award recipients developed a technology capable of transcoding MPEG-2 to H.264 whilst maintaining the quality demanded by broadcasting services, and greatly contributed to the spread of IP broadcasting of digital terrestrial broadcast content over IP networks. Specifically, an MPEG-2/H.264 transcoder device that conformed to the strict guidelines laid down by broadcasting stations (real-time processing with low delay of less than two seconds and preserved image quality as tested through subjective evaluation) was developed and applied to IP rebroadcasting services. Distribution of high-quality terrestrial digital broadcasting content over IP networks without deterioration was contributory, and IP broadcast services now have more than 3 million subscribers.

Furthermore, in order to realize 8K broadcasting which is expected to become the mainstream going forward, it is essential to develop H.265 encoding systems with higher compression ratios. In order to compensate for the performance limit of the processing chip, the researchers established multichip parallel encoding control techniques, thereby making a major contribution to the success of world's first 8K test broadcasting. They developed a one chip 4K H.265 encoder LSI (NARA) that fully exploits the compression performance of H.265 by means of a search algorithm that can adaptively switch search accuracy and search position through statistical processing of motion vectors. By operating the NARA in parallel, 8K/60P encoding compliant with ARIB, which is a Japanese broadcasting operation standard, was realized. In order to reduce degradation of image quality due to parallelization, high-speed data transfer that can transfer reference image data between multiple chips has also been established. These technologies helped to launch 4K IP broadcasting with H.265 and contributed significantly to future cooperation between communication and broadcasting, together with the start of 8K test broadcasting.

As mentioned above, the achievements accumulated over more than 15 years by the award recipients have made it possible to provide high-quality, high-definition video services to anyone. The influence not only on people’s lives but also on the industry is impressive. Based on these technologies, 8K broadcasting is expected to develop into a service promoting communication and broadcasting collaboration.

Fig. 1 MPEG-2/H.264/H.265 codecs usage example

References

- K. Nitta, T. Minami, T. Kondo, and T. Ogura, “Motion Estimation and Compensation Hardware Architecture for a Scene-Adaptive Algorithm on a Single-Chip MPEG-2 Video Encoder,” IEICE Trans. Info. & Sys. , Vol. E84-D, No. 3, pp. 317−325, Mar. 2001.

- K. Nakamura, M. Ikeda, T. Yoshitome, and T. Ogura, “Global rate control scheme for MPEG-2 HDTV parallel encoding system,” Proc. Int'l Conference on Information Technology: Coding and Computing 2000, IEEE CS, pp. 195−200. Mar. 2000.

- K. Nitta, T. Yoshitome, T. Kondo, H. Iwasaki, and J. Naganuma, “Improvement on SIMD Macroblock Processor in MPEG-2 Video Encoder LSI,” IEICE Trans. Electronics, Vol. J87-C, No. 4, pp. 377−385, Apr. 2004.(In Japanese)

- J. Naganuma, H, Iwasaki, K. Nitta, K. Nakamura, T. Yoshitome, M. Ogura, Y. Nakajima, Y. Tashiro, T. Onishi, M. Ikeda, and M. Endo, “VASA: Single-chip MPEG-2 422P@HL CODEC LSI with Multi-chip Configuration for Large Scale Processing beyond HDTV Level,” Hot Chips 14, Aug. 2002.

- T. Onishi, K. Nakamura, T. Yoshitome, and J. Naganuma, “A Distributed Stream Multiplexing Architecture for Multi-Chip Configuration beyond HDTV,” IEICE Trans, Info. & Sys., Vol. E91-D, No.12, pp. 2862- 2867, Dec. 2008.

- T. Onishi, K. Nitta, T. Sano, H. Iwasaki, M. Ikeda, J. Naganuma, and K. Kamikura, “A Motion Estimation and Motion Compensation Architecture for Professional H.264/AVC Encoder LSI,” IEICE Trans. Info. & Sys., Vol. J93-D, No. 10, pp. 2148−2155, Oct. 2010. (In Japanese)

- K. Nitta, H. Iwasaki, T. Onishi, T. Sano, A. Sagata, Y. Nakajima, M. Inamori, R. Tanida, A. Shimizu, K. Nakamura, M. Ikeda, and J. Naganuma, “An H.264/AVC High422 Profile and MPEG-2 422 Profile Encoder LSI for HDTV Broadcasting Infrastructures,” IEICE Trans. on Electronics, Vol. E95-C, No. 4, pp. 432−440, Apr. 2012.

- M. Ikeda, H. Iwasaki, K. Nitta, T. Onishi, T. Sano, A. Sagata, Y. Nakajima, M. Inamori, T. Yoshitome, H, Matsuda, R. Tanida, A. Shimizu, K. Nakamura, and J. Naganuma, “Professional H.264/AVC CODEC Chip-set for High-quality HDTV Broadcast Infrastructure and High-end Flexible CODEC Systems,” Hot Chips 19, Aug. 2007.

- T. Onishi, T. Sano, Y. Nishida, K. Yokohari, Jia Su, K. Nakamura, K. Nitta, K. Kawashima, J. Okakamoto, N. Ono, R. Kusaba, A. Sagata, H. Iwasaki, M. Ikeda, and A. Shimizu, "Single-chip 4K 60fps 4:2:2 HEVC Video Encoder LSI with 8K Scalability," Proc. 2015 IEEE Symposium on VLSI Circuits, pp. 54−55, June 2015.

- H. Iwasaki, T. Onishi, K. Nakamura, K. Nitta, T. Sano, Y. Nishida, K. Yokohari, Jia Su, N. Ono, R. Kusaba, A. Sagata, M. Ikeda, and A. Shimizu, “Professional H.265/HEVC encoder LSI toward high-quality 4K/8K broadcast infrastructure,”, Hot Chips 27, Aug. 2015.