| Pioneering Research on Ultrahigh-Speed Packet Networking Technologies |

| Naoaki Yamanaka, Eiji Oki |

Naoaki Yamanaka |

Eiji Oki |

The recipients pioneered ultrahigh-speed packet-switching networking technologies that form the basis of today’s Internet. Their research covered a variety of networking technologies including the Asynchronous Transfer Mode (ATM), Multi-Protocol Label Switching (MPLS), Generalized MPLS (GMPLS), optical networks, and the Internet. In addition to the contributions to research and development, the recipients took leadership roles in the standardization of and interoperability in the networks.

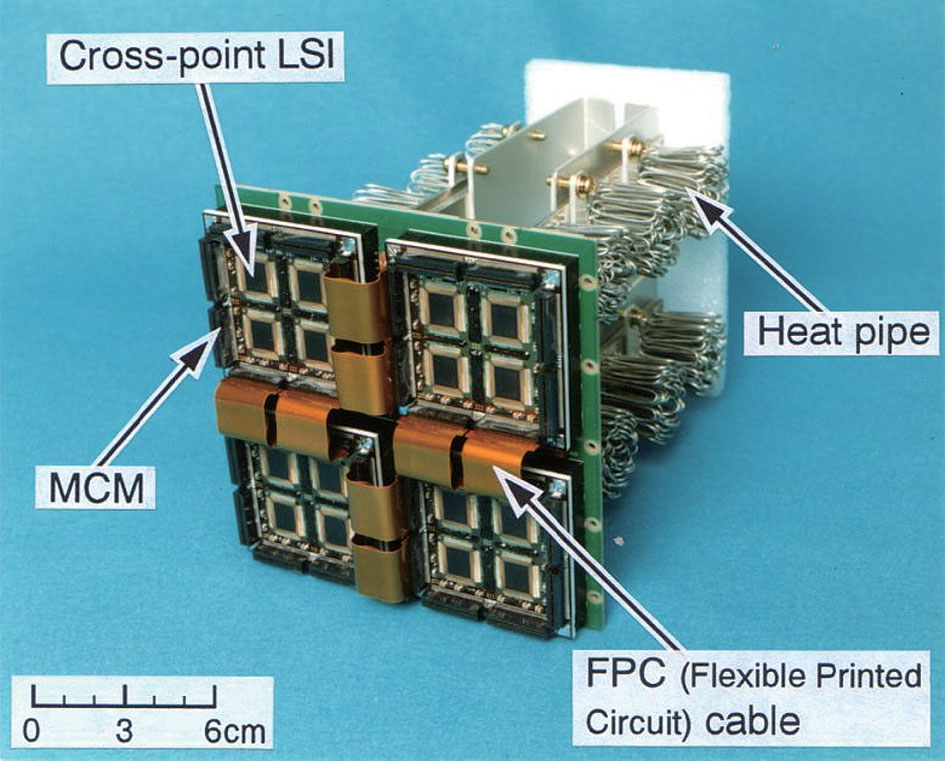

The recipients contributed, theoretically and practically, to switching technologies including packet switch architecture, scheduling, hardware, and systematization [1-5]. By utilizing leading-edge electronic and optical devices and theoretically analyzing traffic behaviors, the recipients integrated advanced electronic and optical technologies to achieve high-speed switching. The recipients invented a switch architecture allowing a high-speed switch LSI to be expanded; the arbitration time does not depend on the number of connected switch LSIs. Combining their invention with leading-edge technologies, including fine-processing CMOS/SIMOX LSI technology, Copper-Polyamide multichip technology, and optical interconnect technology, they successfully developed a switching system that achieved the fastest record in the world at that time. Their contributions were awarded the Best Paper Award of IEEE Transactions on CPMT (1994), Best Paper Awards of IEEE ECTC (1990, 1994, 1998), IEICE Paper Award (1998), and the Telecom System Technology Prize (1994). In addition, one of the recipients as above transferred the developed technologies to overseas enterprises and introduced them to the NTT’s switching system.

Fig. 1 Copper-Polyimide Multichip Module

The gigabit interconnect is realized with Si-bipolar SST technology. Such technology is provided to global venders for constructing to supercomputers and servers.

The gigabit interconnect is realized with Si-bipolar SST technology. Such technology is provided to global venders for constructing to supercomputers and servers.

Fig. 2 OPTIMA: 640Gbps Backbone System (2000)

OPTIMA is realized using new switching architecture and advanced hardware technologies such as fine-pitch CMOS technology, the multichip ceramic module with heat-pipe cooling, and optical interconnection between modules.

Furthermore, in addition to hardware and system technologies, the recipients pioneered the areas of network control and path computation [6-7]. The recipients advocated the concept of separating the path computation element (PCE) from network elements such as routers and optical cross-connects so that network providers can easily and flexibly deploy a control server for multilayer path computation to realize their own policies.

The recipients detailed their original concept and its applications in [6]. In addition, one of the recipient founded Photonic Internet Laboratory (PIL), which was an original advanced model enabling effective linkage among industry, academia, and government, and has taken the leadership on networking interoperability with domestic and international companies for over a decade. The recipients made great efforts towards standardizing protocols in the Internet Engineering Task Force (IETF). Thanks to their efforts, a suite of PCE protocols has been installed in routers and optical cross-connects.OPTIMA is realized using new switching architecture and advanced hardware technologies such as fine-pitch CMOS technology, the multichip ceramic module with heat-pipe cooling, and optical interconnection between modules.

As described above, from the viewpoints of academic, industrial, and technology-dissemination contributions, the recipients have demonstrated their outstanding leadership in the field of ultrahigh-speed packet-switching networking technologies. These achievements were awarded IEEE Fellows (2000, 2013), where one of the recipient has a record as a youngest Japanese person to receive this distinction, and IEICE Fellows (2008, 2013) in addition to the above-mentioned awards. The recipients authored several books [8-10] what were indispensable in systematizing networking technologies from the basics to applications. These achievements are highly outstanding and truly deserving of the IEICE Achievement Award.

- (1)N. Yamanaka, S. Kikuchi, T. Kon, T. Ohsaki, “Multichip 1.8-Gb/s high-speed space-division switching module using copper-polyimide multilayer substrate,” 40th IEEE 40th ECTC CMPT, May 1990.

- (2)N. Yamanaka, K. Endo, K. Genda, H. Fukuda , T. Kishimoto, and S. Sasaki, “320 Gb/s high-speed ATM switching system hardware technologies based on copper-polyimide MCM,” IEEE Trans., CPMT, Part B, vol. 18, no. 1, pp. 83-91, Feb. 1995.

- (3)E. Oki and N. Yamanaka, “A high-speed tandem-crosspoint ATM switch architecture with input and output buffers,” IEICE Trans. Commun., vol. E81-B, no. 2, pp. 215-223, Feb. 1998.

- (4)E. Oki, N. Yamanaka, Y. Ohtomo, and Katsuhiko Okazaki, “A 10-Gb/s (1.25 Gb/s x 8) 4 x 2 0.25-um CMOS/SIMOX ATM switch based on scalable distributed arbitration,” IEEE J. Solid-State Circuits, vol. 34, no. 12, pp. 1921-1934, Dec. 1999.

- (5)N. Yamanaka, E. Oki, S. Yasukawa, R. Kawano, and K. Okazaki, “OPTIMA: scalable, multi-stage, 640-Gbit/s ATM switching system based on advanced electronic and optical WDM technologies,” IEICE Trans. Commun., vol. E83-B, no. 7, pp. 1488-1496, Jul. 2000.

- (6)E. Oki, K. Shiomoto, D. Shimazaki, N. Yamanaka, W. Imajuku, and Y. Takigawa, “Dynamic multilayer routing schemes in GMPLS-based IP+Optical networks,” IEEE Commun. Mag., vol. 43, no. 1, pp. 108-114, Jan. 2005.

- (7)N. Yamanaka, “Photonic Internet Lab.: breakthrough for leading edge photonic-GMPLS (MPLS),” IEICE Trans., vol. E87-B, No. 3, pp. 573-578, Mar. 2004.

- (8) N. Yamanaka, K. Shiomoto, and E. Oki, GMPLS Technologies, CRC Press, Boca Raton, Sep. 2005.

- (9) E. Oki, Linear Programming and Algorithms for Communication Networks, CRC Press, Boca Raton, Aug. 2012.

- (10)N. Yamanaka (Editor), E. Oki, K. Shiomoto, and S. Okamoto (Authors), Internet Backbone Networks, Telecommunication Association, Mar. 2014. (in Japanese)