# An Algorithm for the "Effective Capacitance" of CMOS Gate with Interconnect Load

Zhang-cai Huang<sup>†</sup>, Atsushi Kurokawa<sup>†\*</sup>, Yasuaki Inoue<sup>†</sup>, and Jun-fa Mao<sup>‡</sup>

†Waseda University, Fukuoka, Japan

\*Semiconductor Technology Academic Reaseach Center, Kanagawa, Japan

‡ Shanghai Jiao Tong University, Shanghai, China

Email: hzc\_2002@asagi.waseda.jp

Abstract — In this paper, we propose an algorithm for computing the effective capacitance of CMOS gate with interconnect load in deep submicron technology. Compared with previous methods, the new approach is accurate and does not require pre-simulation table. The experimental results show that it is in agreement with Spice simulation.

## 1. Introduction

With the rapid progress of Integrated Circuit process technology, interconnect wire has become an important factor that influences the performance of chip. In deep submicron technology, interconnect wire delay takes the largest portion of the whole chip delay. Currently, the interconnect resistance is equal or larger than the gate resistance and part of the load capacitance is shielded "seen" from the gate. The RC- $\pi$  load model [1] is used to model a general RC tree because it is found to be accurate sufficiently when compared with actual circuit.

However, the empirical gate-delay equations have only one pure capacitive load  $C_L$ , and the RC- $\pi$  model has three parameters  $C_1$ ,  $C_2$  and R. Therefore, it is difficult to calculate the gate-delay with RC- $\pi$  model. In order to maintain compatibility with the empirical gate-delay model, the effective capacitance  $C_{eff}$  of interconnect load was proposed, which accounts for the reduction in the gate delay due to the shielding component [2].

A number of research papers [3]-[6] have been published on calculating the effective capacitance of interconnect wire. In [4] and [6], the effective capacitance is obtained based on the table of a pre-simulation result. However, these methods need pre-simulation with large storage resource. In [3] and [5], the authors obtain the capacitance value by replacing the driver gate with a resistance in theoretical model. However, the driving resistance in their model is determined by the output load and input transition time. There is a great variation in the above mentioned parameters and therefore one can not

obtain an accurate result.

This paper describes a new algorithm to compute the effective capacitance for interconnect load. The new algorithm is based on the analytical expressions stated in this paper and is considerably accurate without requiring pre-simulation table. The experimental results show it is close to the Spice simulation.

The rest of this paper is organized as follows. Section 2 gives a detailed description of the proposed algorithm to compute the effective capacitance. Results for a 0.25-um CMOS process are presented in Section 3. Finally, conclusions are made in Section 4.

#### 2. Proposed algorithm

#### 2.1. The definition of effective capacitance

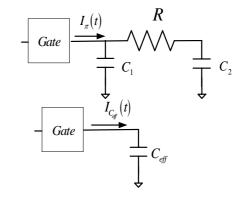

Figure 1 shows the gate driving an RC- $\pi$  load and capacitance  $C_{eff}$  load. The effective capacitance  $C_{eff}$  is defined to be a single capacitance that will results in the same 50% point delay as the RC- $\pi$  model [2]. Then, the value of  $C_{eff}$  is determined by equating the charges transferred to  $C_{eff}$  and to the actual RC- $\pi$  load over the interval, namely between t = 0 and  $t = t_D$  [4],

Fig.1. The gate driving an RC- $\pi$  load and effective capacitance  $C_{\rm eff}$ .

where  $t_D$  is the time of the output voltage from initial

point to 50% point. Therefore, we have

$$\frac{1}{t_D} \int_0^{t_D} I_{\pi}(t) dt = \frac{1}{t_D} \int_0^{t_D} I_{C_{eff}}(t) dt , \qquad (1)$$

where  $I_{\pi}(t)$  is the current flowing into the RC- $\pi$  load in Fig.1, and  $I_{Ceff}(t)$  is the current flowing into the effective capacitance  $C_{eff}$ . Moreover, the LHS of Eq.(1) is the average current flowing into RC- $\pi$  load over the time zero to  $t_D$ , and the RHS is that of  $C_{eff}$ .

#### 2.2. Analytical Expressions

The charge Q from the gate with an average current  $\overline{I}$  flowing into the load over an interval t is given by  $Q = \overline{I}t$ . Therefore, the charge RC-  $\pi$  load  $Q_{\pi}$  now equals the charge the effective capacitance  $Q_{Ceff}$  as indicated in Fig.1.

$$Q_{\pi} = Q_{Ceff} \ . \tag{2}$$

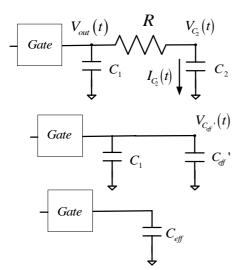

Figure 2 shows that how the effective capacitance is obtained from RC- $\pi$  load. In the figure, we assume the initial charges of all the capacitances are zero. From Fig.2 it can be inferred that  $C_{eff} = C_1 + C_{eff}$ '. Therefore, we have

$$Q_{Ceff} = Q_{C1} + Q_{Ceff'}, \qquad (3)$$

where  $Q_{C1}$  is the charge of capacitance  $C_1$ ,  $Q_{Ceff'}$  is the charge of the capacitance  $C_{eff}'$ . This idea can be extended for the RC- $\pi$  load. Therefore, we obtain that

$$Q_{\pi} = Q_{C1} + Q_{C2}, \qquad (4)$$

Fig.2. Effective capacitance is obtained from RC- $\pi$  load. where  $Q_{C1}$  is the charge of capacitance  $C_1$ ,  $Q_{C2}$  is the

charge of the capacitance  $C_2$ .

Substituting Eqs. (3) and (4) into (2), we have

$$Q_{C2} = Q_{Ceff'}, \tag{5}$$

From the relation Q = CV, where V is the voltage of capacitance C and Q is the charge of capacitance C, Eq.(5) becomes

$$C_2 V_{C2}(t) = C_{eff} V_{Ceff'}(t), \qquad (6)$$

where  $V_{C2}(t)$  is the voltage of capacitance  $C_2$ ,  $V_{Ceff}(t)$  is the voltage of capacitance  $C_{eff}'$ . When  $t = t_D$ ,  $V_{Ceff}(t)$  equals  $V_{out}(t)$ . Therefore,  $C_{eff}'$  can be written as follow [4]:

$$C_{eff}' = \frac{C_2 V_{C2}(t)}{V_{out}(t)} \Big|_{t=t_D} .$$

<sup>(7)</sup>

Applying KVL to RC- $\pi$  load circuit in Fig.2, we obtain

$$RI_{C2}(t) + V_{C2}(t) = V_{out}(t).$$

(8)

The current flowing into capacitance  $C_2$  is

$$I_{C2}(t) = C_2 \frac{dV_{out}(t)}{dt}.$$

(9)

Using Eq.(9), Eq.(8) becomes

$$RC_{2} \frac{dV_{C2}(t)}{dt} + V_{C2}(t) = V_{out}(t).$$

(10)

From Eq.(10),  $V_{C2}(t)$  is expressed as

$$V_{C2}(t) = e^{-\frac{t}{RC_2}} \left[ \frac{1}{RC_2} \int_{o}^{t} V_{out}(t) e^{\frac{t}{RC_2}} dt + k \right], \quad (11)$$

where k is a constant. The condition k = 0 is determined by  $V_{C2}(t)|_{t=0} = 0$ . If  $V_{out}(t)$  is known then we can get  $V_{C2}(t)$ , and  $C_{eff}$ ' can be obtained with Eq.(7).

#### 2.3. Output Waveform

It is well known that the output waveform of the gate  $V_{out}(t)$  changes linearly around the 50% point of the output waveform [7][8][9]. CMOS gates can be modeled using a combination of quadratic and linear functions that correspond to the operating regions of the MOSFET's [10]. Therefore, the output waveform of CMOS gate can be assumed as follows [2]:

$$V_{out}(t) = \begin{cases} V_{initial} - ct^2 & 0 \le t \le t_x \\ a + b(t - t_x) & t_x \le t \le t_D \end{cases}.$$

(12)

Staring at the initial voltage  $V_{initial}$ , the waveform is quadratic to the 20% point  $t_x$ . In Eq.(12),  $V_{initial}$  is equal to  $V_{DD}$  for a falling waveform, and equal to zero for rising waveform. From the 20% point to the midpoint, the transistors are in the active region. Therefore, the waveform is assumed to be linear up to 50% point  $t_D$ . Moreover, a, b and c are the constants, a is equal to  $0.2 V_{DD}$  for rising waveform and  $0.8 V_{DD}$  for falling waveform. The function of output voltage  $V_{out}(t)$  is continuous at  $t = t_x$ . Therefore,

$$b = \frac{0.3V_{DD}}{t_D - t_x} \tag{13}$$

and

$$c = \frac{b}{-2t_x}.$$

(14)

The values of  $t_x$  and  $t_D$  can be determined by using a gate pre-characterization from the output waveform, and expressed as follows [9]:

$$t_D = f\left(t_{in}, C_L\right) \tag{15}$$

and

$$t_x = g\left(t_{in}, C_L\right), \tag{16}$$

where  $t_{in}$  is the input signal transition time from zero to 100% of its steady-state value.

# 2.4. Algorithm for Calculating Effective Capacitance

Using Eqs.(11) and (12),  $V_{C2}(t)$  now becomes

$$V_{C2}(t)|_{t=t_{D}} = \frac{V_{DD}}{2} - \frac{3V_{DD}}{10} \frac{RC_{2}}{t_{D} - t_{x}} + \frac{3}{10} \frac{V_{DD}(RC_{2})^{2}}{t_{x}(t_{D} - t_{x})} e^{-\frac{t_{D} - t_{x}}{RC_{2}}} \left(1 - e^{-\frac{t_{x}}{RC_{2}}}\right).$$

(17)

Since the output voltage is  $V_{out}(t)|_{t=t_D} = V_{DD}/2$ , we obtain the expression of effective capacitance as follow:

$$C_{eff} = C_1 + C_2 \left( 1 - \frac{3}{5} \frac{RC_2}{t_D - t_x} + \frac{3}{5} \frac{(RC_2)^2}{t_x (t_D - t_x)} e^{-\frac{t_D - t_x}{RC_2}} \left( 1 - e^{-\frac{t_x}{RC_2}} \right) \right).$$

(18)

From Eq.(18) we infer that  $C_{eff}$  is  $C_1 + C_2$  when the resistance is zero, and  $C_1$  when the resistance *R* tends to infinity.

We use the following iterative procedure to compute the effective capacitance  $\ C_{\rm eff}$  .

- 1. Set an initial value  $C_{eff} = C_1 + C_2$ .

- 2. Obtain the time  $t_D$  and  $t_x$  using Eqs.(15), and (16) with effective capacitance  $C_{eff}$ .

- 3. Compute a new value of  $C_{eff}$  using the parameters  $t_D$ ,  $t_x$  of step 2.

- 4. Set the above new value equal to  $C_{eff}$  and go back to step 2 until the iteration converges.

This procedure usually converges in three or four iterations. Then, the delay of gate can be obtained using the effective capacitance  $C_{\rm eff}$ .

The effective capacitance  $C_{eff}$  in Eq. (18) is determined in above method. Note that the equation of  $C_{eff}$  in [2] is obtained by substituting Eq. (12) approximated gates output waveform into Eq. (1) directly with an additional approximation which may result in some errors. However, the equation of  $C_{eff}$  in this paper is obtained by substituting Eq.(12) into Eqs.(7) and (11) without additional approximation.

#### **3.** Experimental Results

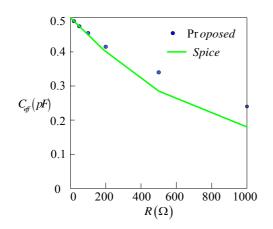

All simulations in this paper are performed for a 0.25-um technology process. Figure 3 gives the comparison between the proposed algorithm and the Spice simulation when the resistance is varied from zero to 1000  $\Omega$ . While performing the simulations the CMOS inverter transistor widths are  $W_n/W_p = 10\mu/21.4\mu$ . Also the values of  $C_1$  and  $C_2$  in the RC- $\pi$  circuit are  $C_1 = 0.1pF/C_2 = 0.4pF$ , and the input signal transition time  $t_r = 200 ps$ .

From Fig.3 we infer that when the resistance becomes larger, the effective capacitance decreases and most of the capacitance of interconnect wire is shielded. For most interconnect wires, the resistance should be much smaller than 1000  $\Omega$  (about 7mm length wires for 0.25-um process). Therefore, the proposed algorithm is accurate.

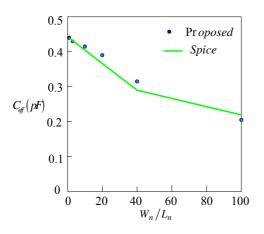

Figure 4 provides the comparison between the proposed algorithm and the Spice simulation when the gate widths are varied from  $W_n/W_p = 0.5\mu/1.07\mu$  to  $W_n/W_p = 25\mu/53.5\mu$ . The ration of the PMOS width to the NMOS width  $W_p/W_n$  always remains at 2.14/1. The values of  $C_1$ ,  $C_2 R$  and R in the RC- $\pi$  circuit are  $C_1 = 0.1pF/C_2 = 0.4pF/R = 300\Omega$ , and the input signal transition time is  $t_t = 200ps$ .

From Fig.4, it is inferred that when the width of gate increases, the effective capacitance decreases. The reason for the decrease in  $C_{eff}$  can be explained from the fact that the gate resistance decreases with increase in the width of transistor. The interconnect wire resistance now

is larger than the gate resistance. Therefore, more capacitance of gate load is shielded by the resistance of the interconnect wire. Therefore, the effective capacitance decreases. Figure 4 shows that the proposed algorithm is close to the Spice simulation result. Especially when the width of transistor is small, the results obtained by using the proposed algorithm have almost same values as the Spice simulation.

Fig.3. Comparison between the proposed algorithm and the Spice simulation when the resistance is varied.

Fig.4. Comparison between the proposed algorithm and the Spice simulation when the gate width is varied.

#### 4. Conclusions

This paper presents an efficient algorithm for calculating the effective capacitance of CMOS gate with interconnect load. Compared with the methods [5], the proposed method does not require pre-simulation table. In addition, the proposed method is more accurate than that [2]. The results of our proposed algorithm are in agreement with the Spice simulation.

## References

- P. R. O'Brien and T. L. Savarino, "Modeling the driving-point characteristic of resistive interconnect for accurate delay estimation," *Proc. int. Conf. Computer-Aided Design*, pp. 512 – 515, Nov. 1989.

- [2] Jessica Qian, Satyamurthy Pullela, and Lawrence Pillage, "Modeling the "effective capacitance" for the RC interconnect of CMOS gates," *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, vol.13, pp. 1526-1535, Dec. 1994.

- [3] A. B. Kahng and S. Muddu, "Improved effective capacitance computations for use in logic and layout optimization," *Proc. of the 12<sup>th</sup> International Conference on VLSI Design*, pp. 578-582, Jan. 1999.

- [4] M. Hafed, M. Oulmane, and N. C. Rumin, "Delay and current estimation in a CMOS inverter with an RC load," *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, vol.20, pp. 80-89, Jan. 2001.

- [5] R. Macys and S. McCormick, "A new algorithm for computing the "effective capacitance" in deep submicron circuits," *Proc. of IEEE Custom Integrated Circuits Conference*, pp. 313-316, May 1998.

- [6] Soroush Abbaspour and Massoud Pedram, "Calculating the effective capacitance for the RC interconnect in VDSM technology," *Proc. of IEEE Asia and South Pacific Design Automation Conference*, pp. 43-48, Jan. 2003.

- [7] Jan M. Rabaey, Digit Integrated circuits: A Design Perspective, Englewood Cliffs, NJ: Prentice-Hall, 1996.

- [8] T. Sakurai and R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas," *IEEE Journal of Solid-State Circuits*, vol.25, pp. 548-594, Apr. 1990.

- [9] F. Dartu, N. Menezes, and L. T. Pillage, "Performance computation for precharacterized CMOS gates with *RC* loads," *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, vol. 15, pp. 544-553, May 1996.